# 3D Magnetic Position Sensor IC

## FEATURES AND BENEFITS

- 3D magnetic sensor enables flexible mechanical integration for contactless linear and rotary position applications

- Configurable signal path processing and on-chip angle calculation for accurate 360° and short stroke (<360°) rotary applications

- Multiple programmable linearization options for maximum measurement accuracy:

- Piecewise-linear and binning modes

- Up to 33-point fixed position

- Up to 22-point programmable positions

- Ratiometric Analog, PWM, or SENT (SAE J2716) output formats

- Integrated IC diagnostics for high reliability

- Developed in accordance with ISO 26262 requirements for hardware product development for use in safety-critical applications

- Supports operation in harsh conditions, required for automotive and industrial applications

- AEC-Q100 Grade 0 qualified

- -40°C to 150°C temperature range

- 4.5 to 5.5 V supply operating range

- Over- and reverse-voltage protection

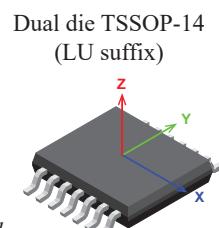

- Multiple package options available:

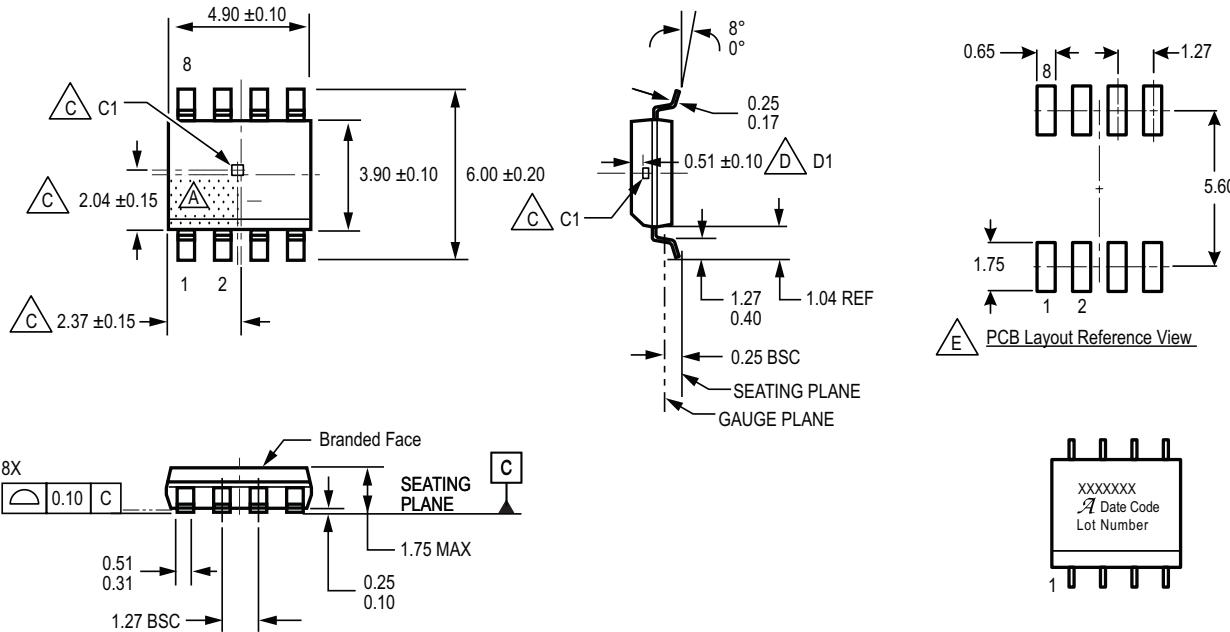

- Single die surface mount (SOIC-8)

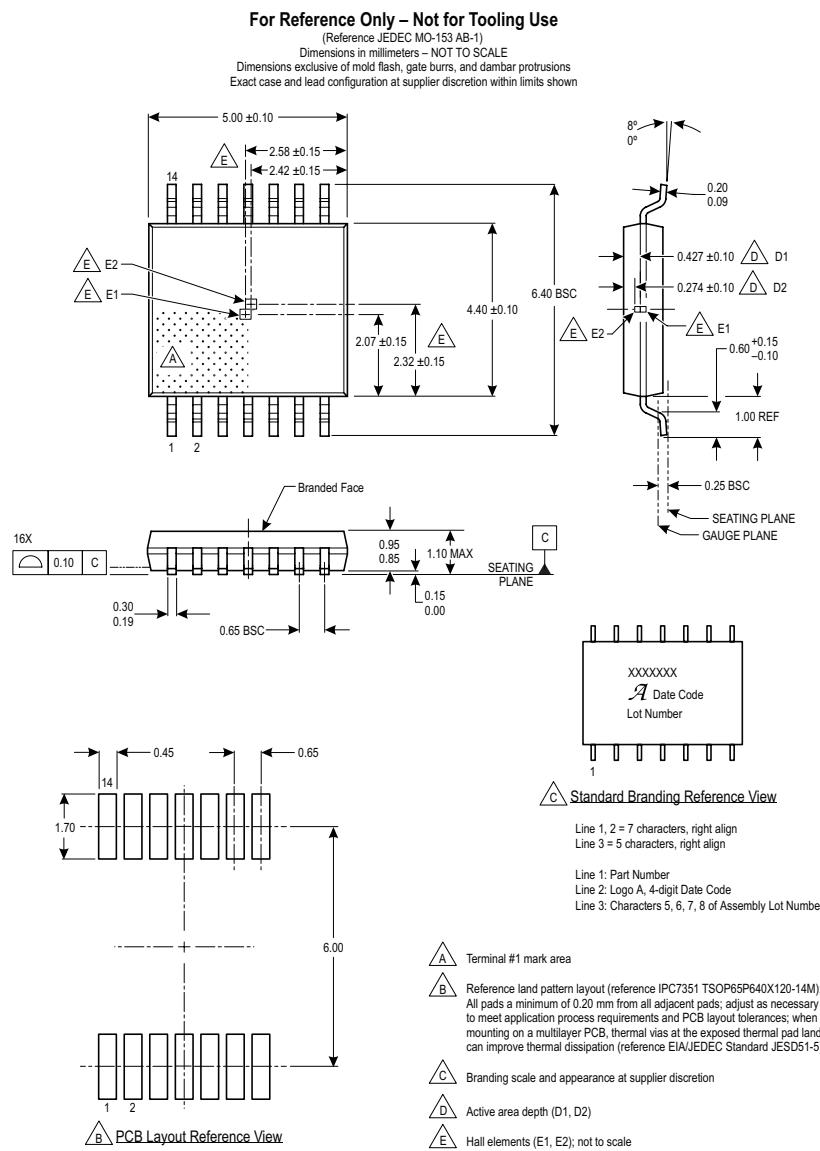

- Dual (full redundant) stacked die surface mount (TSSOP-14)

## APPLICATIONS

- Contact-less linear and rotary position sensor

- Throttle, valve, and cylinder position sensor

- Pedal position sensor

- Transmission position (fork/clutch, shifter, park lock)

## PACKAGES

## DESCRIPTION

The A31315 3DMAG™ position sensor is designed for on-axis and off-axis rotary as well as linear stroke position measurement in automotive, industrial, and consumer applications.

This sensor integrates vertical and planar Hall-effect elements with precision temperature-compensating circuitry to detect two out of three magnetic field components (X, Y, and Z). Using configurable signal processing, linearization, and angle calculation allows the A31315 to accurately resolve the absolute rotary (full 360° and short-stroke <360°) or linear position of a moving magnetic target.

The A31315 features ratiometric analog, PWM, or SENT (SAE J2716) interface options to output the angle between the two factory-selected axes or the field from a single axis. In addition, the SENT interface provides the option to output the field measurement from both channels.

On-chip EEPROM technology, capable of supporting up to 100 write cycles, is integrated for flexible programming of configuration and calibration parameters and includes 92 bits provided for customer device identification purposes.

The A31315 contains on-chip diagnostic features required for high reliability automotive applications, including monitors of both internal and external fault conditions.

Developed in accordance with ISO 26262 as a hardware safety element out of context (SEooC) with ASIL B (single die) and ASIL D (dual die) capability for use in automotive safety-related systems when integrated and used in the manner prescribed in the applicable safety manual and datasheet.

The A31315 is available as a single die in the SOIC-8 package and stacked dual die in the TSSOP-14 package for applications that require full redundancy.

## SELECTION GUIDE [1]

| Part Number             | Die Configuration and Package | Output Interface   | Channel A | Channel B | Maximum Field (G) | Packing                     |

|-------------------------|-------------------------------|--------------------|-----------|-----------|-------------------|-----------------------------|

| A31315LOLATR-XZ-S-SE-10 | Single Die SOIC-8             | SENT (PWM) [2]     | X         | Z         | 1000              | 3,000 pieces per 13-in reel |

| A31315LOLATR-XY-S-SE-10 |                               |                    | X         | Y         | 1000              |                             |

| A31315LOLATR-XZ-S-AR-10 |                               | Analog Ratiometric | X         | Z         | 1000              |                             |

| A31315LOLATR-XY-S-AR-10 |                               |                    | X         | Y         | 1000              |                             |

| A31315LLUBTR-XZ-S-SE-10 | Dual Stacked Die TSSOP-14     | SENT (PWM) [2]     | X         | Z         | 1000              | 4,000 pieces per 13-in reel |

| A31315LLUBTR-XY-S-SE-10 |                               |                    | X         | Y         | 1000              |                             |

| A31315LLUBTR-XZ-S-AR-10 |                               | Analog Ratiometric | X         | Z         | 1000              |                             |

| A31315LLUBTR-XY-S-AR-10 |                               |                    | X         | Y         | 1000              |                             |

[1] Contact Allegro for other axis and field range trim options.

[2] SENT interface is enabled by default. PWM is selectable through customer accessible registers.

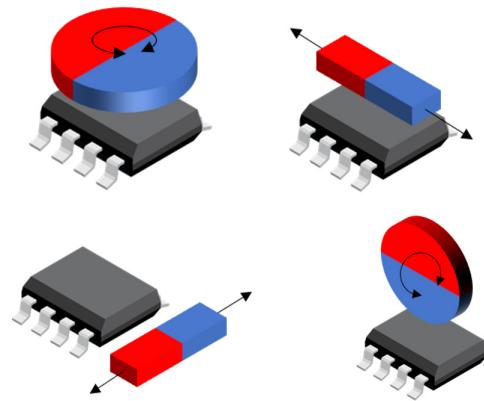

## Part Number Guide

## Table of Contents

|                                                                      |     |

|----------------------------------------------------------------------|-----|

| Features and Benefits.....                                           | 1   |

| Description.....                                                     | 1   |

| Packages.....                                                        | 1   |

| Selection Guide .....                                                | 2   |

| Absolute Maximum Ratings.....                                        | 4   |

| Thermal Characteristics.....                                         | 4   |

| Functional Block Diagram.....                                        | 5   |

| Pinout Diagrams and Terminal Lists .....                             | 6   |

| Application Circuit.....                                             | 7   |

| Digital Output Modes.....                                            | 7   |

| Analog Output.....                                                   | 7   |

| Operating Characteristics .....                                      | 8   |

| Performance Characteristics .....                                    | 9   |

| Interface Characteristics .....                                      | 11  |

| Functional Description .....                                         | 14  |

| Typical Application Information .....                                | 14  |

| Temperature Output.....                                              | 14  |

| Signal Path .....                                                    | 16  |

| 1-D Signal Path .....                                                | 16  |

| Factory Channel A / Channel B Input Selection.....                   | 16  |

| Factory Range Selection.....                                         | 16  |

| Factory Trimming .....                                               | 16  |

| Customer-controllable data path.....                                 | 16  |

| Customer Trimming .....                                              | 16  |

| Low-pass filter .....                                                | 16  |

| Sensor Output During Low-Pass Filter Initialization.....             | 17  |

| Orthogonality Correction .....                                       | 17  |

| Polarity, Offset, Sensitivity, And Temperature Calibration .....     | 18  |

| Polarity Correction .....                                            | 19  |

| Sensitivity Adjustment .....                                         | 19  |

| Sensitivity Correction Over Temperature .....                        | 19  |

| Customer Offset Correction .....                                     | 19  |

| Customer Offset Correction Over Temperature .....                    | 19  |

| Hysteresis Filter .....                                              | 20  |

| Direct Output Register .....                                         | 20  |

| ATAN Input Selection .....                                           | 20  |

| Angle Sign (Rotation Direction).....                                 | 21  |

| Pre-gain Angle Offset Correction .....                               | 21  |

| Angle Gain Correction.....                                           | 21  |

| Post Gain Angle Offset Correction .....                              | 22  |

| Linearization and Binning.....                                       | 23  |

| Linearization / Binning Mode Selection.....                          | 23  |

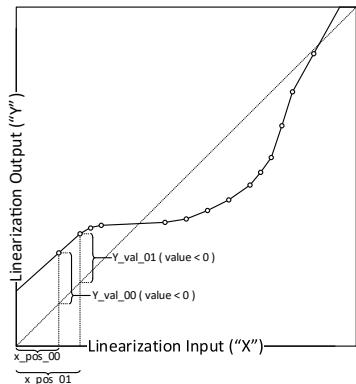

| Fixed Segment Linearization (lin_sel 0).....                         | 24  |

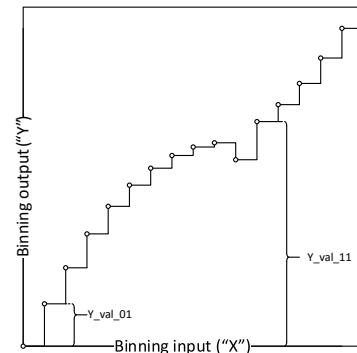

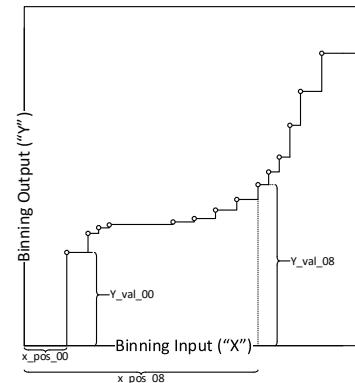

| Fixed Segment Binning (lin_sel 1) .....                              | 24  |

| Variable Segment Linearization (lin_sel 2).....                      | 25  |

| Variable Segment Binning (lin_sel 3) .....                           | 25  |

| Linearization/Binning Parameter Storage .....                        | 26  |

| Number of Linearization / Binning Points.....                        | 27  |

| Binning Mode Hysteresis .....                                        | 27  |

| Output Clamps.....                                                   | 27  |

| Output Protocols.....                                                | 28  |

| Analog Output Mode.....                                              | 28  |

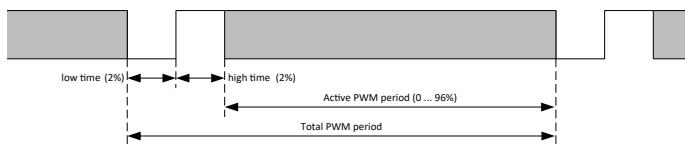

| PWM Output Mode .....                                                | 28  |

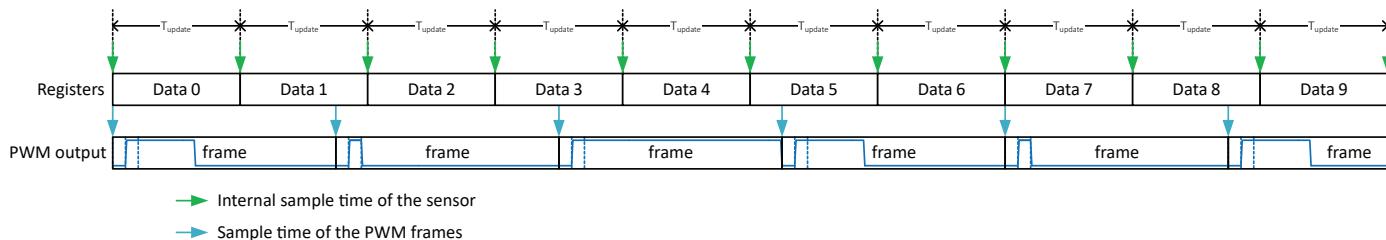

| PWM Sampling Time .....                                              | 28  |

| SENT Output Mode .....                                               | 29  |

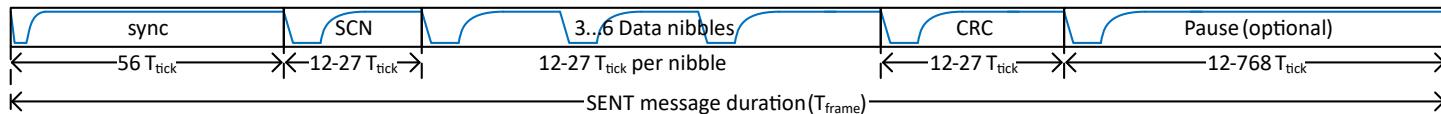

| Message Structure .....                                              | 29  |

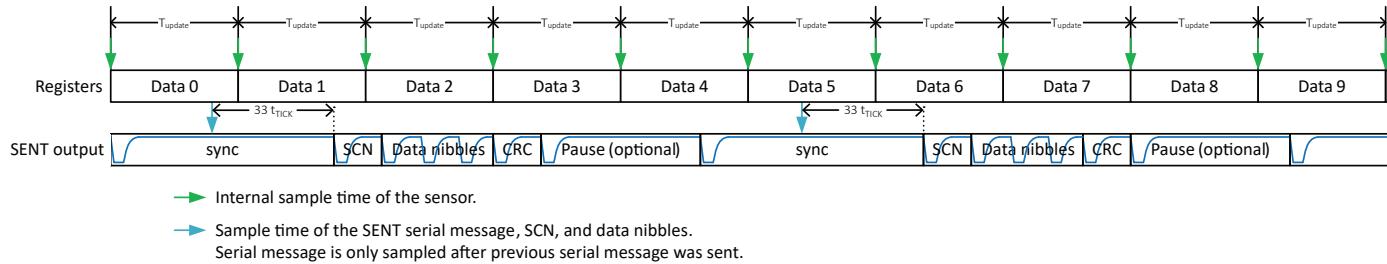

| SENT Sampling Time .....                                             | 30  |

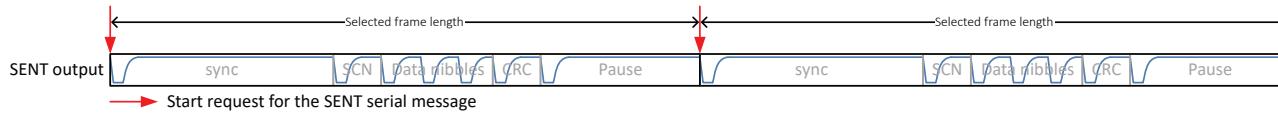

| SENT Output Rate.....                                                | 30  |

| Optional SENT Slow Serial Output Protocol.....                       | 31  |

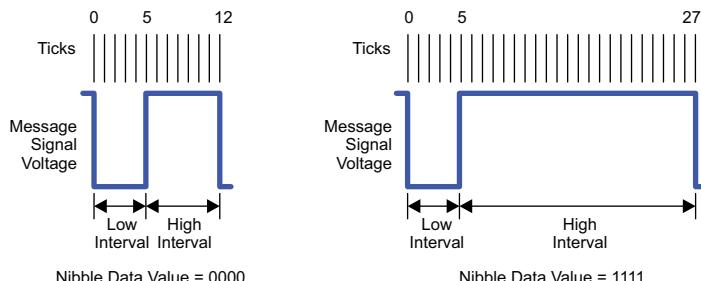

| Data Nibble Format .....                                             | 32  |

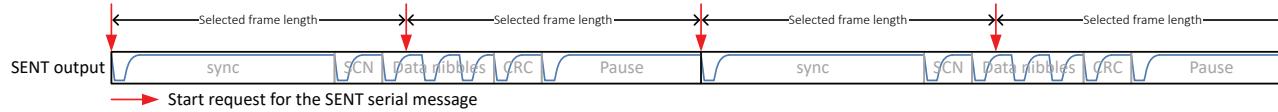

| SENT CRC .....                                                       | 33  |

| SENT Serial Message 6-Bit CRC .....                                  | 33  |

| SENT Message Frame Definitions .....                                 | 35  |

| Error Indicators / Specific Messages / Initialization Message        |     |

| in SENT Output Codes .....                                           | 36  |

| SAE J2716 SENT .....                                                 | 36  |

| SENT Initialization Code Selection .....                             | 36  |

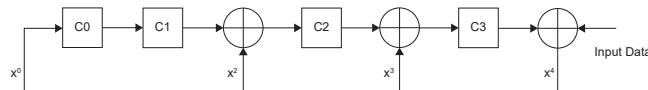

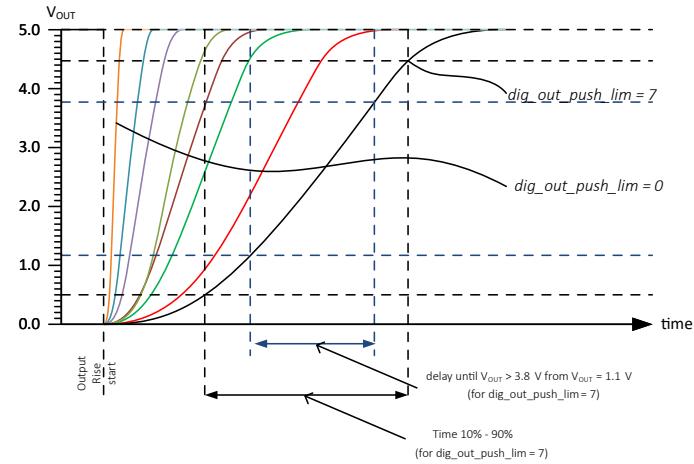

| Digital Output Pin Drive Strength Options .....                      | 37  |

| Output Pin Fall Time Selection.....                                  | 37  |

| Push-pull output setting for SENT and PWM rising edge .....          | 38  |

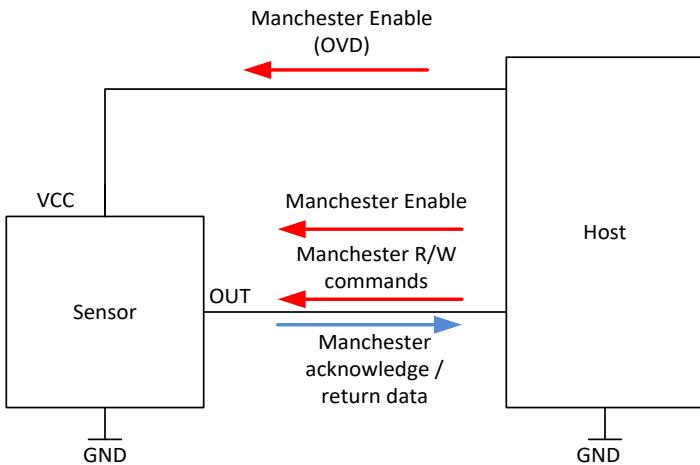

| Programming Protocol .....                                           | 39  |

| Physical Layer .....                                                 | 39  |

| Settings Controlling the Manchester Communication .....              | 39  |

| Entering Manchester Communication Mode Through Analog Output.....    | 39  |

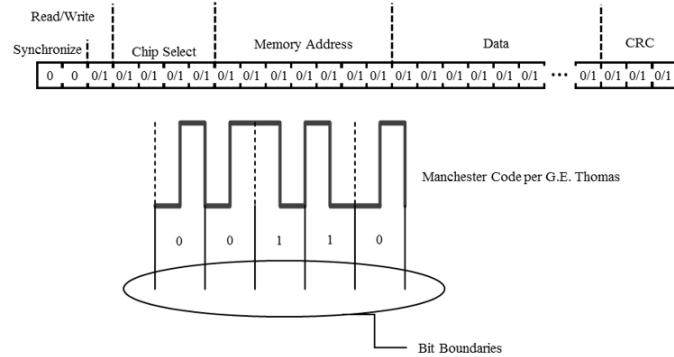

| Serial Interface Message Structure.....                              | 40  |

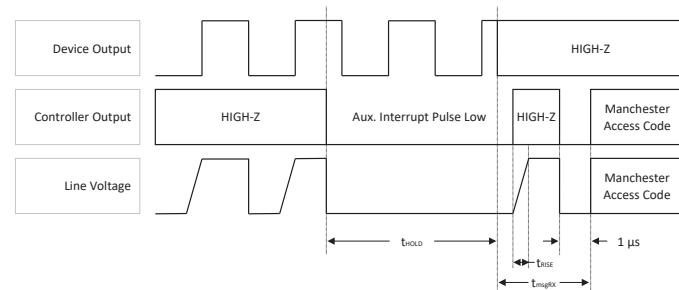

| Manchester Unlocking – SENT/PWM Mode via OVD.....                    | 41  |

| Manchester Unlocking – SENT/PWM Mode via Triggering Pulses.....      | 41  |

| Manchester Unlocking – Analog Mode via OVD                           |     |

| if (ana_lock = 1'b1) and (ana_manch_lock = 1'b1).....                | 42  |

| Manchester Unlocking - Analog Mode via OVD                           |     |

| if (ana_lock = 1'b1) and (ana_manch_lock = 1'b0).....                | 42  |

| Manchester Unlocking – Analog Mode without OVD                       |     |

| if (ana_lock = 1'b0) and (ana_manch_lock = 1'b1).....                | 42  |

| Manchester Unlocking – Analog Mode                                   |     |

| without OVD (ana_lock = 1'b0) and (ana_manch_lock = 1'b0).....       | 42  |

| Manchester Communication CRC .....                                   | 43  |

| EEPROM Lock .....                                                    | 43  |

| EEPROM Margin Checking .....                                         | 43  |

| Error Flag Registers .....                                           | 44  |

| Analog Check Failure (ACF) .....                                     | 44  |

| Angle Outside Clamp (AOC) .....                                      | 44  |

| Temperature Error (TSE) .....                                        | 44  |

| Saturation Flag (SAT) .....                                          | 44  |

| Oscillator Frequency Error (OFE) .....                               | 45  |

| Signal Processing Logic Failure (SLF) .....                          | 45  |

| Signal Radius Out of Range (SRR) .....                               | 45  |

| Power-On Reset (POR) .....                                           | 45  |

| EEPROM Multiple Bit Error (EUE) and EEPROM Single Bit Error (ESE) .. | 45  |

| Shadow Parity Error (SPE) .....                                      | 46  |

| Undervoltage Detection (UVD) .....                                   | 46  |

| Overvoltage Detection (OVD) .....                                    | 46  |

| SENT Output Error Reporting .....                                    | 46  |

| PWM Output Error Reporting .....                                     | 47  |

| Analog Output Error Reporting .....                                  | 47  |

| Broken Wire Detection .....                                          | 47  |

| Logic Built-In Self-Test (LBIST) .....                               | 47  |

| Diagnostic Setting and Clearing .....                                | 50  |

| Memory Access .....                                                  | 50  |

| Shadow Memory Read and Write Transactions .....                      | 50  |

| Package Outline Drawings .....                                       | 64  |

| Appendix A: Specification Definitions .....                          | A-1 |

## ABSOLUTE MAXIMUM RATINGS

| Characteristic                         | Symbol                      | Notes                                                                                                  | Rating     | Unit |

|----------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------|------------|------|

| Forward Supply Voltage                 | $V_{CC(\text{absmax})}$     | Supply is clamped with 20 V limit to GND                                                               | 18         | V    |

| Reverse Supply Voltage                 | $V_{RCC(\text{absmax})}$    | Supply is clamped with -20 V limit to GND                                                              | -18        | V    |

| Forward $V_{OUT}-V_{CC}$ Voltage       | $V_{OUT-CC(\text{absmax})}$ | $V_{OUT}$ is clamped with 20 V limit to $V_{CC}$ ;<br>Note: There is no reverse $V_{OUT}-V_{CC}$ clamp | 18         | V    |

| Forward Output Voltage                 | $V_{OUT(\text{absmax})}$    | Output is clamped with 20 V limit to GND                                                               | 18         | V    |

| Reverse Output Voltage                 | $V_{ROUT(\text{absmax})}$   | Output is clamped with -10 V limit to GND                                                              | -6         | V    |

| Forward Supply Current                 | $I_{CC}$                    |                                                                                                        | 30         | mA   |

| Reverse Supply Current                 | $I_{RCC}$                   |                                                                                                        | -30        | mA   |

| Output Current Limit                   | $I_{OUT(\text{SOURCE})}$    | $V_{OUT}$ shorted to GND                                                                               | 30         | mA   |

|                                        | $I_{OUT(\text{SINK})}$      | $V_{CC}$ shorted to $V_{OUT}$                                                                          | -30        | mA   |

| Extended Operating Ambient Temperature | $T_{A(\text{EXT})}$         | Device will work within this temperature range, but performance is not specified                       | -45 to 165 | °C   |

| Maximum Junction Temperature           | $T_{J(\text{MAX})}$         |                                                                                                        | 165        | °C   |

| Storage Temperature                    | $T_{stg}$                   |                                                                                                        | -65 to 165 | °C   |

## THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol    | Test Conditions* | Value | Unit |

|----------------------------|-----------|------------------|-------|------|

| Package Thermal Resistance | $R_{eJA}$ | SOIC-8           | 125   | °C/W |

|                            |           | TSSOP-14         | 214   | °C/W |

\*Additional thermal information available on the Allegro website.

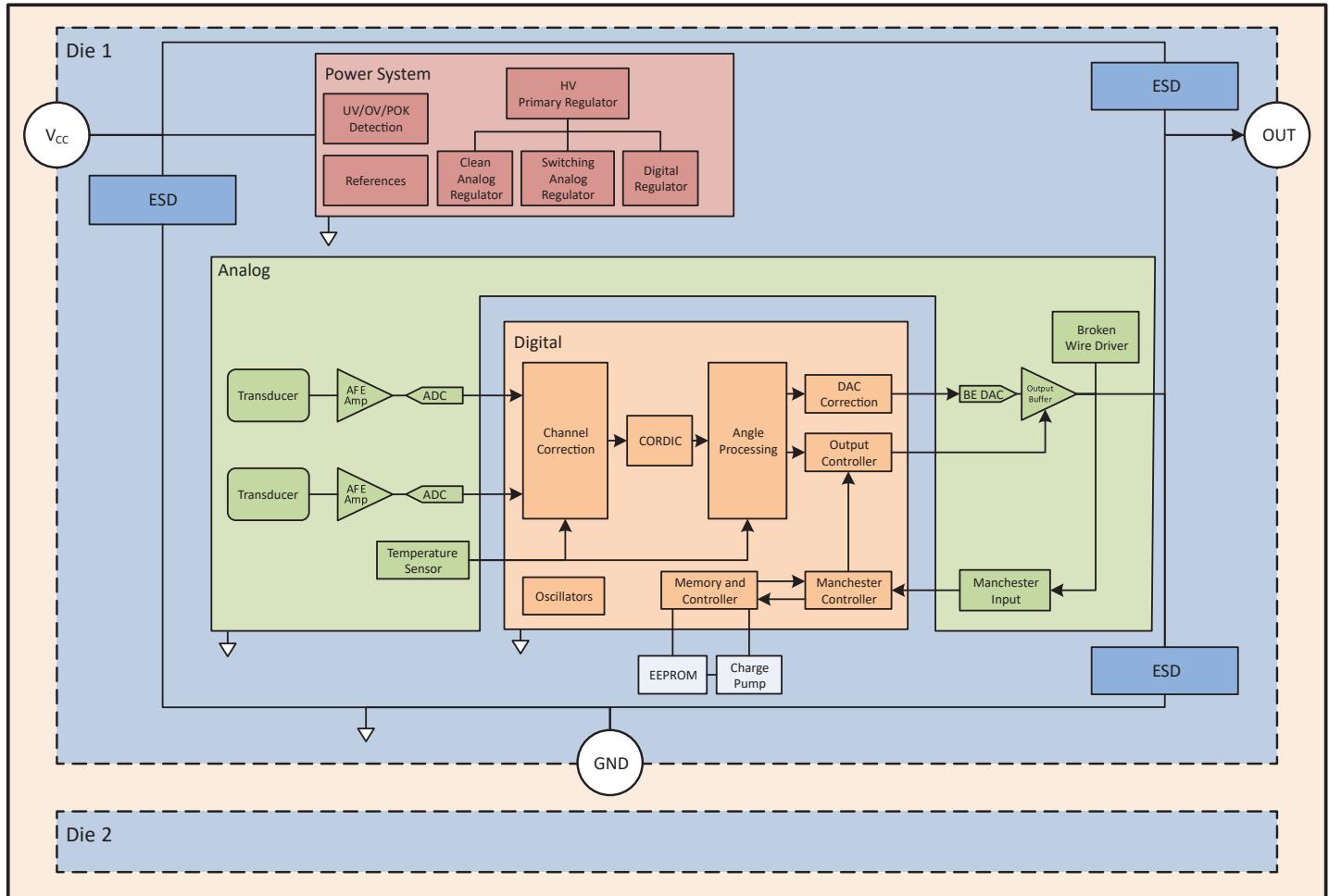

Figure 1: Functional Block Diagram

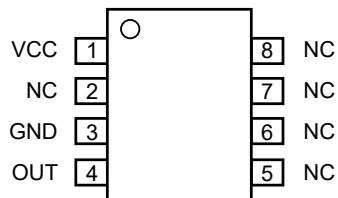

## PINOUT DIAGRAMS AND TERMINAL LISTS

## 8-Pin SOIC Terminal List

| Number | Name | Function          |

|--------|------|-------------------|

| 1      | VCC  | Supply voltage    |

| 2      | NC   | Not connected [1] |

| 3      | GND  | Ground            |

| 4      | OUT  | Device output     |

| 5-8    | NC   | Not connected [1] |

[1] Connect to GND for optimal ESD performance.

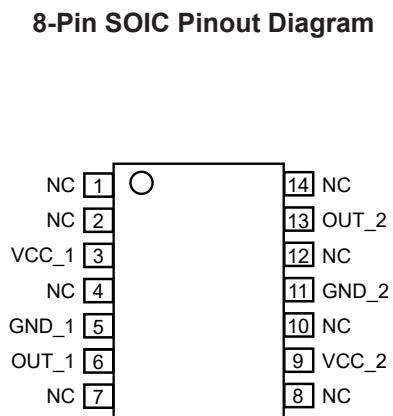

## 14-Pin TSSOP Terminal List

| Number | Name  | Die | Function          |

|--------|-------|-----|-------------------|

| 1-2    | NC    | 1   | Not connected [1] |

| 3      | VCC_1 | 1   | Supply voltage    |

| 4      | NC    | 1   | Not connected [1] |

| 5      | GND_1 | 1   | Ground            |

| 6      | OUT_1 | 1   | Device Output     |

| 7      | NC    | 1   | Not connected [1] |

| 8      | NC    | 2   | Not connected [1] |

| 9      | VCC_2 | 2   | Supply voltage    |

| 10     | NC    | 2   | Not connected [1] |

| 11     | GND_2 | 2   | Ground            |

| 12     | NC    | 2   | Not connected [1] |

| 13     | OUT_2 | 2   | Device Output     |

| 14     | NC    | 2   | Not connected [1] |

[1] Connect to GND for optimal ESD performance.

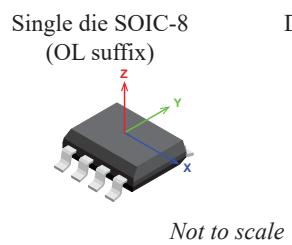

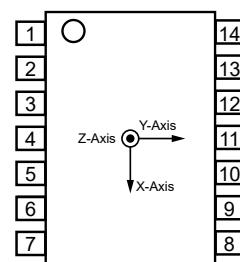

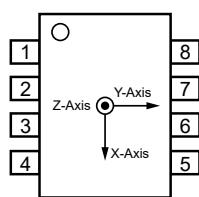

## AXIS DEFINITIONS

Note: Arrows show the default polarity of each axis. Polarity can be changed with internal settings.

## APPLICATION CIRCUIT

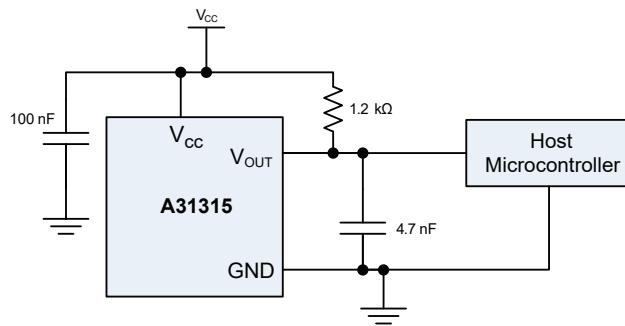

## Digital Output Modes

When using the A31315 in digital output modes, either SENT or PWM, both push-pull and open-drain output drive modes are selectable. Regardless of the selected drive style, a pull-up resistor is still recommended in order to provide a known diagnostic state in the event of a line break or device tri-state event. The figure below shows a typical application circuit for the A31315 when using a digital interface. It should be noted that the capacitance value shown assumes the total capacitance of passive component and capacitance due to harness connections.

Figure 2: A31315 Typical Application Circuit for Digital Output Modes (SENT / PWM)

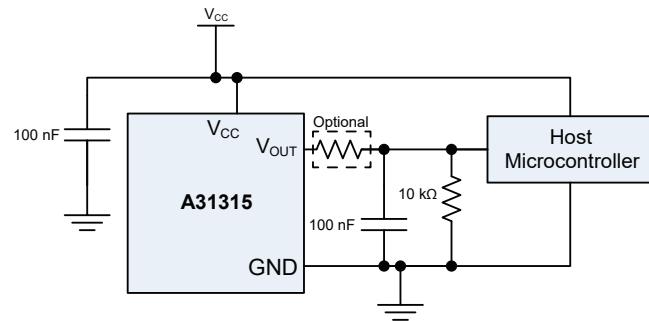

## Analog Output

When using the analog mode of the A31315, capacitance is required for stability of the output. A load resistor, either to GND or V<sub>CC</sub> is recommended, as with the digital interface to provide a known diagnostic state in the event of a line break or device tri-state event. For additional filtering and lower noise, a series resistor can be placed prior to the capacitance to create a low-pass filter. However, caution should be taken, as this will also reduce the operating output voltage based on the ratio of the filter resistor and the load resistance. Additionally, the A31315's analog output mode is ratiometric with V<sub>CC</sub>; for this reason, the host controller monitoring the output voltage should be connected to the same voltage supply as the A31315. A typical application circuit is shown below for using the A31315 as an analog interface.

Figure 3: A31315 Typical Application Circuit for Analog Output Modes

## OPERATING CHARACTERISTICS

| Characteristics                | Symbol       | Test Conditions                                                                                                        | Min. | Typ.      | Max.       | Unit   |

|--------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------|------|-----------|------------|--------|

| <b>ELECTRICAL REQUIREMENTS</b> |              |                                                                                                                        |      |           |            |        |

| Supply Voltage                 | $V_{CC}$     |                                                                                                                        | 4.5  | 5.0       | 5.5        | V      |

| Supply Buffer Capacitor        | $C_{SUP}$    |                                                                                                                        | 10   | 100       | 600        | nF     |

| Supply Current                 | $I_{CC}$     | Each die                                                                                                               | 5.0  | 8.5       | 10.0       | mA     |

| <b>DEVICE REQUIREMENTS</b>     |              |                                                                                                                        |      |           |            |        |

| Ambient Operating Temperature  | $T_A$        |                                                                                                                        | -40  | -         | 150        | °C     |

| Number of EEPROM Writes [1]    | $N_{EEPROM}$ | $T_A = 25^\circ\text{C}$                                                                                               | -    | -         | 100        | writes |

| <b>MAGNETIC REQUIREMENTS</b>   |              |                                                                                                                        |      |           |            |        |

| Magnetic Flux Density          | $ B_{IN} $   | For xxx-10 parts, devices tested at $ B_{IN}  = 300$ G, operation below this value is characterized, but not specified | -    | $\pm 300$ | $\pm 1000$ | G      |

[1] EEPROM writes are not supported at temperatures above 85°C.

**PERFORMANCE CHARACTERISTICS:** Valid for all electrical and device requirements ranges and  $|B_{IN}| \geq 300$  G, unless otherwise noted

| Characteristics                          | Symbol                 | Test Conditions                                                                                    | Min.          | Typ.       | Max.   | Unit    |                       |

|------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------|---------------|------------|--------|---------|-----------------------|

| <b>DEVICE SPECIFICATIONS</b>             |                        |                                                                                                    |               |            |        |         |                       |

| Undervoltage Detection Threshold         | $V_{UVF}$ (LOW, FALL)  | $V_{CC}$ falling, $uvd\_sel = '0'$                                                                 | 3.6           | —          | 4.1    | V       |                       |

|                                          | $V_{UVF}$ (LOW, RISE)  | $V_{CC}$ rising, $uvd\_sel = '0'$                                                                  | 3.7           | —          | 4.2    | V       |                       |

|                                          | $V_{UVF}$ (HIGH, FALL) | $V_{CC}$ falling, $uvd\_sel = '1'$                                                                 | 4.1           | —          | 4.4    | V       |                       |

|                                          | $V_{UVF}$ (HIGH, RISE) | $V_{CC}$ rising, $uvd\_sel = '1'$                                                                  | 4.2           | —          | 4.5    | V       |                       |

| Overvoltage Detection Threshold          | $V_{OVD}$ (LOW, FALL)  | $V_{CC}$ falling, $ovd\_sel = '1'$                                                                 | 5.6           | —          | 6.0    | V       |                       |

|                                          | $V_{OVD}$ (LOW, RISE)  | $V_{CC}$ rising, $ovd\_sel = '1'$                                                                  | 5.65          | —          | 6.05   | V       |                       |

|                                          | $V_{OVD}$ (HIGH, FALL) | $V_{CC}$ falling, $ovd\_sel = '0'$                                                                 | 8.4           | —          | 10.2   | V       |                       |

|                                          | $V_{OVD}$ (HIGH, RISE) | $V_{CC}$ rising, $ovd\_sel = '0'$                                                                  | 8.6           | —          | 10.4   | V       |                       |

| Power-On Reset Voltage                   | $V_{POR(FALL)}$        | $V_{CC}$ falling                                                                                   | 2.6           | —          | 2.9    | V       |                       |

|                                          | $V_{POR(RISE)}$        | $V_{CC}$ rising                                                                                    | 2.8           | —          | 3.1    | V       |                       |

| Power-On Time                            | $t_{PO}$               | Time from $V_{CC} > V_{CC(MIN)}$ until unfiltered output is settled                                | —             | 1.0        | 1.7    | ms      |                       |

| Oscillator Frequency                     | $f_{OSC}$              |                                                                                                    | 7.36          | 8.00       | 8.64   | MHz     |                       |

| <b>ABSOLUTE ANGLE SPECIFICATIONS [1]</b> |                        |                                                                                                    |               |            |        |         |                       |

| Angle Error (XY)                         | $ERR_{ANG(XY)}$        | $T_A = 25^\circ\text{C}$ [2]                                                                       | —1.0          | —          | 1.0    | degrees |                       |

|                                          |                        | $-40 \leq T_A \leq 150^\circ\text{C}$                                                              | —1.2          | —          | 1.2    | degrees |                       |

|                                          |                        | After AEC-Q100 Grade 0 Qual Stress, $T_A = -40^\circ\text{C}, 25^\circ\text{C}, 150^\circ\text{C}$ | —             | $\pm 0.65$ | —      | degrees |                       |

| Angle Error (XZ)                         | $ERR_{ANG(XZ)}$        | $T_A = 25^\circ\text{C}$ [2]                                                                       | —1.0          | —          | 1.0    | degrees |                       |

|                                          |                        | $-40 \leq T_A \leq 150^\circ\text{C}$                                                              | —1.2          | —          | 1.2    | degrees |                       |

|                                          |                        | After AEC-Q100 Grade 0 Qual Stress, $T_A = -40^\circ\text{C}, 25^\circ\text{C}, 150^\circ\text{C}$ | —             | $\pm 0.93$ | —      | degrees |                       |

| Input-Referred Angle Noise               | $N_{ANG(IN)}$          | $ B_{IN}  = \pm 300$ G input field                                                                 | $bw\_sel = 0$ | —          | 0.0291 | —       | degree <sub>RMS</sub> |

|                                          |                        |                                                                                                    | $bw\_sel = 1$ | —          | 0.0291 | —       | degree <sub>RMS</sub> |

|                                          |                        |                                                                                                    | $bw\_sel = 2$ | —          | 0.0326 | —       | degree <sub>RMS</sub> |

|                                          |                        |                                                                                                    | $bw\_sel = 3$ | —          | 0.0381 | —       | degree <sub>RMS</sub> |

|                                          |                        |                                                                                                    | $bw\_sel = 4$ | —          | 0.0468 | —       | degree <sub>RMS</sub> |

|                                          |                        |                                                                                                    | $bw\_sel = 5$ | —          | 0.0575 | —       | degree <sub>RMS</sub> |

|                                          |                        |                                                                                                    | $bw\_sel = 6$ | —          | 0.0673 | —       | degree <sub>RMS</sub> |

| <b>ANGLE DRIFT SPECIFICATIONS [1]</b>    |                        |                                                                                                    |               |            |        |         |                       |

| Angle Drift (XY)                         | $DRIFT_{Ang,Temp(XY)}$ | Change in angle relative to $T_A = 25^\circ\text{C}$ [2]                                           | —1.2          | —          | 1.2    | degrees |                       |

|                                          | $DRIFT_{Ang,Life(XY)}$ | Change in angle relative to pre-stress conditions [4]                                              | —1.3          | $\pm 0.40$ | 1.3    | degrees |                       |

| Angle Drift (XZ)                         | $DRIFT_{Ang,Temp(XZ)}$ | Change in angle relative to $T_A = 25^\circ\text{C}$ [2]                                           | —1.2          | —          | 1.2    | degrees |                       |

|                                          | $DRIFT_{Ang,Life(XZ)}$ | Change in angle relative to pre-stress conditions [4]                                              | —1.33         | $\pm 0.91$ | 1.33   | degrees |                       |

Continued on next page...

**PERFORMANCE CHARACTERISTICS (continued):** Valid for all electrical and device requirements ranges and  $|B_{IN}| \geq 300$  G, unless otherwise noted

| Characteristics                            | Symbol                          | Test Conditions                                             | Min.  | Typ.   | Max. | Unit         |

|--------------------------------------------|---------------------------------|-------------------------------------------------------------|-------|--------|------|--------------|

| <b>ABSOLUTE CHANNEL SPECIFICATIONS [1]</b> |                                 |                                                             |       |        |      |              |

| Default Channel Sensitivity                | SENS <sub>Target</sub>          | Selection Guide Part Number: XXX-10                         | –     | 32.125 | –    | LSB / G      |

| Channel Sensitivity Error (X,Y)            | ERR <sub>Sens(X,Y)</sub>        | T <sub>A</sub> = 25°C [2]                                   | –1.5  | –      | 1.5  | %            |

|                                            |                                 | –40 ≤ T <sub>A</sub> ≤ 150°C                                | –3    | –      | 3    | %            |

| Channel Sensitivity Error (Z)              | ERR <sub>Sens(Z)</sub>          | T <sub>A</sub> = 25°C [2]                                   | –1.5  | –      | 1.5  | %            |

|                                            |                                 | –40 ≤ T <sub>A</sub> ≤ 150°C                                | –4    | –      | 4    | %            |

| Channel Offset Error (X,Y)                 | ERR <sub>Off(X,Y)</sub>         | T <sub>A</sub> = 25°C [2]                                   | –1.5  | –      | 1.5  | G            |

|                                            |                                 | –40 ≤ T <sub>A</sub> ≤ 150°C                                | –4    | –      | 4    | G            |

| Channel Offset Error (Z)                   | ERR <sub>Off(Z)</sub>           | T <sub>A</sub> = 25°C [2]                                   | –1.5  | –      | 1.5  | G            |

|                                            |                                 | –40 ≤ T <sub>A</sub> ≤ 150°C                                | –1.5  | –      | 1.5  | G            |

| Channel Linearity Error (X,Y)              | ERR <sub>Lin(X,Y)</sub>         | 100 G ≤ B <sub>IN</sub> ≤ 1000 G                            | –0.3  | –      | 0.3  | %            |

| Channel Linearity Error (Z)                | ERR <sub>Lin(Z)</sub>           | 100 G ≤ B <sub>IN</sub> ≤ 1000 G                            | –0.3  | –      | 0.3  | %            |

| Input-Referred Channel Noise (X,Y)         | N <sub>CHAN(X,Y)</sub>          | T <sub>A</sub> = 25°C                                       | –     | 5.245  | –    | mG (RMS/√Hz) |

|                                            |                                 | –40 ≤ T <sub>A</sub> ≤ 150°C                                | –     | 7.821  | –    | mG (RMS/√Hz) |

| Input-Referred Channel Noise (Z)           | N <sub>CHAN(Z)</sub>            | T <sub>A</sub> = 25°C                                       | –     | 2.083  | –    | mG (RMS/√Hz) |

|                                            |                                 | –40 ≤ T <sub>A</sub> ≤ 150°C                                | –     | 3.104  | –    | mG (RMS/√Hz) |

| <b>CHANNEL DRIFT SPECIFICATIONS [1]</b>    |                                 |                                                             |       |        |      |              |

| Channel Sensitivity Error Drift (X,Y)      | DRIFT <sub>Sens,Temp(X,Y)</sub> | Change in sensitivity relative to T <sub>A</sub> = 25°C [2] | –2    | –      | 2    | %            |

|                                            | DRIFT <sub>Sens,Life(X,Y)</sub> | Change in sensitivity relative to pre-stress conditions [4] | –2.50 | ±1.3   | 2.50 | %            |

| Channel Sensitivity Error Drift (Z)        | DRIFT <sub>Sens,Temp(Z)</sub>   | Change in sensitivity relative to T <sub>A</sub> = 25°C [2] | –3    | –      | 3    | %            |

|                                            | DRIFT <sub>Sens,Life(Z)</sub>   | Change in sensitivity relative to pre-stress conditions [4] | –3.50 | ±2.5   | 3.50 | %            |

| Channel Offset Drift (X,Y)                 | DRIFT <sub>Off,Temp(X,Y)</sub>  | Change in offset relative to T <sub>A</sub> = 25°C [2]      | –3.5  | –      | 3.5  | G            |

|                                            | DRIFT <sub>Off,Life(X,Y)</sub>  | Change in offset relative to pre-stress conditions [4]      | –0.90 | ±0.25  | 0.90 | G            |

| Channel Offset Drift (Z)                   | DRIFT <sub>Off,Temp(Z)</sub>    | Change in offset relative to T <sub>A</sub> = 25°C [2]      | –1.5  | –      | 1.5  | G            |

|                                            | DRIFT <sub>Off,Life(Z)</sub>    | Change in offset relative to pre-stress conditions [4]      | –0.60 | ±0.5   | 0.60 | G            |

[1] As measured through digital interface with factory trim. Values do not include DAC or account for customer trim registers.

[2] 25°C measurements taken after 48-72 hour wait at 40-55% relative humidity.

[3] Parameter not measured at final test. Determined by design and characterization.

[4] Min and Max values based on worst case drift seen during Q100 qual.

**INTERFACE CHARACTERISTICS:** Valid for all electrical and device requirements ranges and  $|B_{IN}| \geq 300$  G, unless otherwise noted

| Characteristics                               | Symbol              | Test Conditions                                                                                                   | Min.  | Typ.  | Max.             | Unit |

|-----------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------|-------|-------|------------------|------|

| Broken Wire Response Time                     | $t_{BW}$            | Time after $V_{CC} - GND = 0.2$ V, either $V_{CC}$ or GND wire broken, $C_L = 100$ nF, $C_{SUP} = 100$ nF         | —     | —     | 500              | μs   |

| High-Z Leakage                                | $I_{leak(Hi-Z)}$    | Device in High-Z mode, output shorted to GND or VCC                                                               | -10   | —     | 10               | μA   |

| Filter Step Response Time                     | $t_{RESP}$          | $bw\_sel = 5$ , time to 90% response to step                                                                      | —     | 396   | 450              | μs   |

| Angle Update Rate                             | $t_{UPDATE}$        | Valid for all bandwidth settings                                                                                  | 14.72 | 16    | 17.28            | μs   |

| <b>MANCHESTER INTERFACE SPECIFICATIONS</b>    |                     |                                                                                                                   |       |       |                  |      |

| Manchester Input Thresholds <sup>[3]</sup>    | $V_{trig(H)}$       | $V_{OUT}$ rising, $dig\_comm\_input\_high = '0'$                                                                  | 1.800 | 1.980 | 2.160            | V    |

|                                               |                     | $V_{OUT}$ rising, $dig\_comm\_input\_high = '1'$                                                                  | 2.185 | 2.365 | 2.540            | V    |

|                                               | $V_{trig(L)}$       | $V_{OUT}$ falling, $dig\_comm\_input\_low = '0'$                                                                  | 0.830 | 0.990 | 1.155            | V    |

|                                               |                     | $V_{OUT}$ falling, $dig\_comm\_input\_low = '1'$                                                                  | 1.385 | 1.640 | 1.905            | V    |

|                                               | $V_{trig(hys)}$     | $dig\_comm\_input\_high = '0'$ , $dig\_comm\_input\_low = '0'$                                                    | 0.815 | 0.985 | 1.150            | V    |

|                                               |                     | $dig\_comm\_input\_high = '0'$ , $dig\_comm\_input\_low = '1'$                                                    | 0.160 | 0.335 | 0.525            | V    |

|                                               |                     | $dig\_comm\_input\_high = '1'$ , $dig\_comm\_input\_low = '0'$                                                    | 1.155 | 1.380 | 1.605            | V    |

|                                               |                     | $dig\_comm\_input\_high = '1'$ , $dig\_comm\_input\_low = '1'$                                                    | 0.495 | 0.725 | 0.995            | V    |

| Manchester Communication Speed <sup>[3]</sup> | $f_{MAN}$           | Manchester input bit rate (from host to sensor)                                                                   | 4.0   | —     | 100              | kbps |

|                                               |                     | Manchester output bit rate with 100 nF load (device responds at the input bit rate)                               | 4.0   | —     | 8 <sup>[1]</sup> | kbps |

| <b>SENT INTERFACE SPECIFICATIONS</b>          |                     |                                                                                                                   |       |       |                  |      |

| SENT Tick Time                                | $t_{TICK}$          | Valid for all SENT Modes, $dig\_out\_data\_rate = '0'$                                                            | 2.76  | 3     | 3.24             | μs   |

|                                               |                     | Valid for all SENT Modes, range of selectable tick times <sup>[2]</sup>                                           | 0.5   | —     | 10               | μs   |

| SENT Tick Time Tolerance                      | $TOL_{TICK}$        | Valid for all selectable tick times                                                                               | -8    | —     | 8                | %    |

| SENT Output Resolution                        | $RES_{SENT}$        | Based on $sent\_data\_sel$                                                                                        | 12    | —     | 16               | bits |

| SENT Output Saturation Voltage                | $V_{SAT(LOW)}$      | Output current = -4.7 mA, $V_{CC} = 5$ V, output FET on                                                           | —     | —     | 0.55             | V    |

| SENT Output Load Capacitance                  | $C_L$               |                                                                                                                   | —     | 4.7   | 5.7              | nF   |

| SENT Output Load Resistance                   | $R_{L(PULLUP)}$     | Output Current $\geq -10$ mA                                                                                      | 1.2   | —     | —                | kΩ   |

| SENT Output Low Voltage <sup>[3]</sup>        | $V_{OL}$            | Low state voltage with 0.52 mA DC load current                                                                    | —     | —     | 0.5              | V    |

| SENT Output High Voltage <sup>[3]</sup>       | $V_{OH}$            | High state voltage with 0.1 mA DC load current                                                                    | 4.1   | —     | —                | V    |

| SENT Ground Current <sup>[3]</sup>            | $I_{GND}$           | Average current through (signal) ground line over one message                                                     | —     | —     | 50               | mA   |

| SENT Supply Ripple Current <sup>[3]</sup>     | $I_{SUP-RIPPLE}$    | Peak-to-peak variation in supply current consumption over one message at frequencies up to $f_C = 30$ kHz         | —     | —     | 9.0              | mA   |

| SENT Fall Time <sup>[3]</sup>                 | $t_{FALL}$          | From $V_{OUT} = 3.8$ V to $V_{OUT} = 1.1$ V, $I_{GND} \leq 20$ mA, 3 μs tick time                                 | —     | —     | 6.5              | μs   |

|                                               |                     | From $V_{OUT} = 3.8$ V to $V_{OUT} = 1.1$ V, 20 mA $\leq I_{GND} \leq 50$ mA, 3 μs tick time                      | —     | —     | 5.0              | μs   |

| SENT Rise Time <sup>[3]</sup>                 | $t_{RISE}$          | From $V_{OUT} = 1.1$ V to $V_{OUT} = 3.8$ V, 3 μs tick time                                                       | —     | —     | 18               | μs   |

| SENT Edge Jitter <sup>[3]</sup>               | $\Delta t_{FALL}$   | Edge to edge jitter with static environment for any pulse prior, 3 μs tick time                                   | —     | —     | 0.1              | μs   |

| SENT Nibble Jitter <sup>[3]</sup>             | $\Delta t_{NIBBLE}$ | Variation of maximum nibble time compared to the expected time derived from the calibration pulse, 3 μs tick time | —     | —     | 0.3              | μs   |

Continued on next page...

**INTERFACE CHARACTERISTICS (continued):** Valid for all electrical and device requirements ranges and  $|B_{IN}| \geq 300$  G, unless otherwise noted

| Characteristics                       | Symbol              | Test Conditions                                        | Min.                   | Typ.    | Max.    | Unit              |            |

|---------------------------------------|---------------------|--------------------------------------------------------|------------------------|---------|---------|-------------------|------------|

| <b>PWM INTERFACE SPECIFICATION</b>    |                     |                                                        |                        |         |         |                   |            |

| PWM Carrier Frequency                 | $f_{PWM}$           | See Table 10                                           | 125                    | —       | 16000   | Hz                |            |

| PWM Carrier Frequency Tolerance       | $TOL(f_{PWM})$      |                                                        | —8                     | —       | 8       | %                 |            |

| PWM Resolution                        | $RES_{PWM}$         | Based on $f_{PWM}$                                     | 8                      | —       | 15      | bit               |            |

| PWM Jitter                            | $PWM_{JIT}$         | $f_{PWM} \geq 2$ kHz, see Table 10 for LSB definition  | —1                     | —       | 1       | LSB               |            |

|                                       |                     | $f_{PWM} < 2$ kHz, see Table 10 for LSB definition     | —3                     | —       | 3       | LSB               |            |

| PWM Duty Cycle                        | $D_{PWM}$           |                                                        | 2                      | —       | 98      | %                 |            |

| PWM Saturation Voltage                | $V_{SAT(LOW)}$      | $R_{PULLUP} \geq 1.2$ k $\Omega$                       | —                      | —       | 0.35    | V                 |            |

| PWM Load Capacitance                  | $C_L$               |                                                        | —                      | —       | 4.7     | nF                |            |

| PWM Load Resistance                   | $R_{L(PULLUP)}$     |                                                        | 1.2                    | —       | —       | k $\Omega$        |            |

| <b>ANALOG INTERFACE SPECIFICATION</b> |                     |                                                        |                        |         |         |                   |            |

| DAC DNL <sup>[3]</sup>                | DNL                 | $V_{CC} = 5$ V                                         | —0.022                 | —       | 0.022   | % $V_{CC}$        |            |

| DAC INL <sup>[3]</sup>                | INL                 | $V_{CC} = 5$ V                                         | —0.098                 | —       | 0.098   | % $V_{CC}$        |            |

| DAC Ratiometry                        | RAT                 | $V_{OUT} = 8$ to 92 % $V_{CC}$                         | —0.2                   | —       | 0.2     | %                 |            |

| DAC Gain Error                        | $Gain_{DAC}$        | $V_{CC} = 5$ V                                         | —0.2                   | —       | 0.2     | %                 |            |

| DAC Offset Error                      | $Off_{DAC}$         | $V_{CC} = 5$ V, $T_A = 25^\circ\text{C}$               | —3                     | —       | 3       | mV                |            |

|                                       |                     | $V_{CC} = 5$ V                                         | —8                     | —       | 8       | mV                |            |

| DAC Noise <sup>[3]</sup>              | $N_{DAC}$           | $V_{CC} = 5$ V, BW = 12 kHz, Outputting fixed DAC code | —                      | 0.37    | —       | mV <sub>RMS</sub> |            |

| Analog Resolution                     | $RES_{DAC}$         |                                                        | —                      | 12      | —       | bits              |            |

| Step Size                             | $STEP_{DAC}$        | Step size of DAC                                       | 0.01391                | 0.01465 | 0.01538 | % $V_{CC}$        |            |

| Saturation Voltage                    | $V_{SAT(HIGH)}$     | $R_L = 4.7$ k $\Omega$                                 | 93                     | —       | —       | % $V_{CC}$        |            |

|                                       | $V_{SAT(LOW)}$      | $R_L = 4.7$ k $\Omega$                                 | —                      | —       | 7       | % $V_{CC}$        |            |

|                                       | $V_{SAT(HIGH)}$     | $R_L = 10$ k $\Omega$                                  | 95                     | —       | —       | % $V_{CC}$        |            |

|                                       | $V_{SAT(LOW)}$      | $R_L = 10$ k $\Omega$                                  | —                      | —       | 5       | % $V_{CC}$        |            |

| Operating Voltage Range               | $V_{OH}$            | $R_L = 4.7$ k $\Omega$ , linearity error < 0.1 %       | 92                     | —       | —       | % $V_{CC}$        |            |

|                                       | $V_{OL}$            | $R_L = 4.7$ k $\Omega$ , linearity error < 0.1 %       | —                      | —       | 8       | % $V_{CC}$        |            |

|                                       | $V_{OH}$            | $R_L = 10$ k $\Omega$ , linearity error < 0.1 %        | 94                     | —       | —       | % $V_{CC}$        |            |

|                                       | $V_{OL}$            | $R_L = 10$ k $\Omega$ , linearity error < 0.1 %        | —                      | —       | 6       | % $V_{CC}$        |            |

| Diagnostic Voltage ranges             | $V_{SATDIAG(HIGH)}$ | $V_{CC} = 5$ V                                         | $R_L = 3.3$ k $\Omega$ | 94      | 98      | 100               | % $V_{CC}$ |

|                                       |                     |                                                        | $R_L = 5$ k $\Omega$   | 96      | 98      | 100               | % $V_{CC}$ |

|                                       |                     |                                                        | $R_L = 10$ k $\Omega$  | 97      | 98      | 100               | % $V_{CC}$ |

|                                       | $V_{SATDIAG(LOW)}$  | $V_{CC} = 5$ V                                         | $R_L = 3.3$ k $\Omega$ | 0       | 2       | 6                 | % $V_{CC}$ |

|                                       |                     |                                                        | $R_L = 5$ k $\Omega$   | 0       | 2       | 4                 | % $V_{CC}$ |

|                                       |                     |                                                        | $R_L = 10$ k $\Omega$  | 0       | 2       | 3                 | % $V_{CC}$ |

Continued on next page...

**INTERFACE CHARACTERISTICS (continued):** Valid for all electrical and device requirements ranges and  $|B_{IN}| \geq 300$  G, unless otherwise noted

| Characteristics                       | Symbol          | Test Conditions                                                                                   |                     | Min.  | Typ.  | Max.  | Unit       |

|---------------------------------------|-----------------|---------------------------------------------------------------------------------------------------|---------------------|-------|-------|-------|------------|

| <b>ANALOG INTERFACE SPECIFICATION</b> |                 |                                                                                                   |                     |       |       |       |            |

| Analog Low Operating Range            | $V_{LIMOUT(L)}$ | $V_{CC} = 5$ V                                                                                    | ana_range_sel = '0' | 0.000 | 0.000 | 0.014 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '1' | 0.186 | 0.200 | 0.214 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '2' | 0.236 | 0.250 | 0.264 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '3' | 0.286 | 0.300 | 0.314 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '4' | 0.336 | 0.350 | 0.364 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '5' | 0.386 | 0.400 | 0.414 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '6' | 0.486 | 0.500 | 0.514 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '7' | 0.736 | 0.750 | 0.764 | V          |

| Analog High Operating Range           | $V_{LIMOUT(H)}$ | $V_{CC} = 5$ V                                                                                    | ana_range_sel = '0' | 4.986 | 5     | 5     | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '1' | 4.786 | 4.8   | 4.814 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '2' | 4.736 | 4.75  | 4.764 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '3' | 4.686 | 4.7   | 4.714 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '4' | 4.636 | 4.65  | 4.664 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '5' | 4.586 | 4.6   | 4.614 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '6' | 4.486 | 4.5   | 4.514 | V          |

|                                       |                 |                                                                                                   | ana_range_sel = '7' | 4.236 | 4.25  | 4.264 | V          |

| Load Capacitance <sup>[3]</sup>       | $C_L$           | ana_cap_sel = '0'                                                                                 |                     | 10    | –     | 150   | nF         |

|                                       |                 | ana_cap_sel = '2', recommended for $C_L \geq 100$ nF                                              |                     | 50    | –     | 480   | nF         |

|                                       |                 | ana_cap_sel = '4', recommended for $C_L \geq 400$ nF                                              |                     | 300   | –     | 600   | nF         |

| Load Resistance                       | $R_L$           | Pull-up to VCC or pull-down to GND                                                                |                     | 4.23  | –     | –     | k $\Omega$ |

| Analog Response Time <sup>[3]</sup>   | $t_{RESP}$      | Sensor output with 100 nF load 1482 Hz bandwidth, time from 90% input change to 90% output change |                     | –     | –     | 600   | $\mu$ s    |

<sup>[1]</sup> Based on receiver design.

<sup>[2]</sup> Tick times under 0.5  $\mu$ s are available, but not guaranteed.

<sup>[3]</sup> Parameter not measured at final test. Determined by design and characterization.

## FUNCTIONAL DESCRIPTION

The A31315 contains two independent signal paths. Each channel has dedicated polarity, sensitivity and offset correction that is available to the customer for end-of-line calibration. This allows the A31315 to be used in both rotary and linear position applications in any mounting orientation relative to the sensing magnet, and to provide high accuracy and matching as the device and magnetic system changes over temperature.

The A31315 features an internal CORDIC calculation of angle from factory-selected pair of detection axes (X, Y, and Z). The CORDIC calculation effective accuracy is 16 bits. Optionally, the A31315 can function as a 1-D sensor by bypassing the CORDIC calculation. See Equation 12 for exact implementation. This mode is also resolved at a 16-bit resolution.

Equation 1:

$$\theta = \text{atan2}(\sin(\theta), \cos(\theta))$$

The output angle value is available in SENT, PWM, or analog output options. Alternatively, the two factory-selected channels of the X, Y, and Z channels are available to output in SENT. Along with the magnetic data, the SENT option provides access to additional device information such as temperature, error flag information, and customer identification register data. End-of-line angle calibration options are available in customer space to allow the device to be used in a wide number of contactless sensing applications.

## Typical Application Information

The A31315 has a high level of customer programmability to be used in a number of applications for either on- or off-axis rotary angle or linear position sensing. For on-axis rotary sensing, the on-chip ATAN2 provides an angle output that, combined with the configurable update rate, allows magnetic angular sensing at a wide range of system bandwidth requirements. To help account for errors associated with off-axis mounting of the sensor, the individual channel sensitivity and offset correction can be used to match the signals input to the ATAN2.

The A31315 can be used for slide-by applications where a one-dimensional position change of a target is to be measured. The angle output from the A31315 is related to the linear position of the magnetic target. With the available linearization on the A31315, stroke lengths greater than the length of the magnet can be realized.

## Temperature Output

The A31315 temperature sensor output that is used for temperature compensation within the device can be read from primary register temperature\_16b, or in SENT in the extended data nibbles or SCN serial message.

Table 1: Temperature Output Options

| Temperature Reporting Method       | Code Range         | Temperature Range   | Step Size | Conversion                                                                               |

|------------------------------------|--------------------|---------------------|-----------|------------------------------------------------------------------------------------------|

| Read of Register (temperature_16b) | -32,768 ... 32,767 | -231.0 ... 281.0°C  | 1/8°C     | $T_A [^{\circ}\text{C}] = \frac{\text{signed 16-bit temperature code}}{128} + 25$        |

| SENT Serial or Extended Nibble     | 1 ... 4088         | -230.9 ... 280.0 °C | 1/8°C     | $T_A [^{\circ}\text{C}] = \frac{\text{unsigned 12-bit temperature code} - 2048}{8} + 25$ |

| SENT 8-BIT Temperature Data        | 1 ... 255          | -229.0... 279.0 °C  | 2°C       | $T_A [^{\circ}\text{C}] = (\text{unsigned 8-bit temperature code} - 128) \times 2 + 25$  |

SENT temperature sensor output corresponds to SAEJ2716 APRIL2016, chapter E.2.2.3, with the following function representation:

SENT Serial or Extended Nibble:

$$X_1 = -230.875^{\circ}\text{C} = 42.275 \text{ K}$$

$$Y_1 = 1$$

$$X_2 = +280.000^{\circ}\text{C} = 553.150 \text{ K}$$

$$Y_2 = 4088$$

SENT 8-Bit Data:

$$X_1 = -229.0^{\circ}\text{C} = 44.150 \text{ K}$$

$$Y_1 = 1$$

$$X_2 = +279.000^{\circ}\text{C} = 552.150 \text{ K}$$

$$Y_2 = 255$$

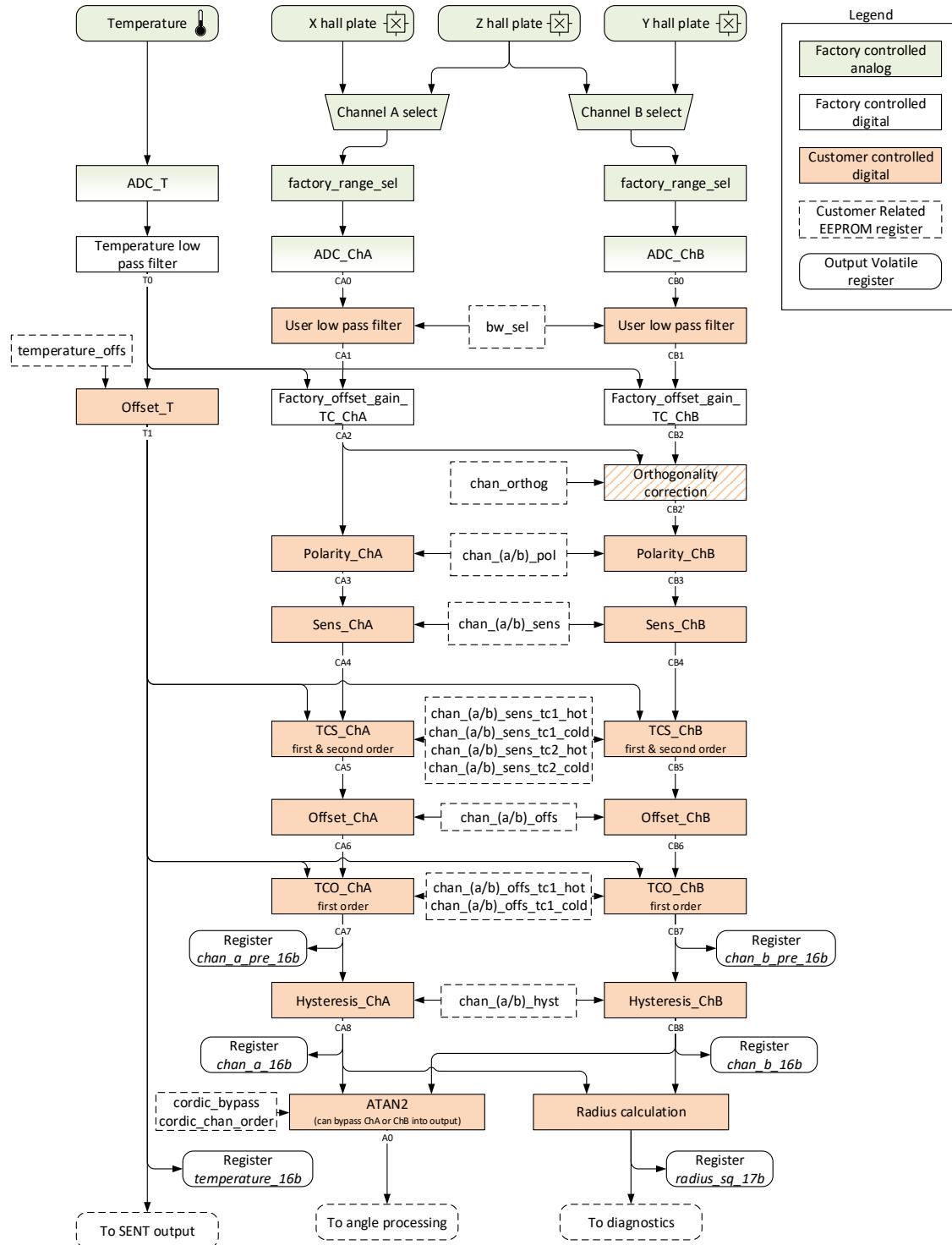

Figure 4: 1D Signal Path Processing Flow

## Signal Path

The A31315 signal path contains two main sections. The first is two 1-D signal paths each reflecting the magnetic field in one direction as specified in the selection guide. The second section uses a CORDIC calculation to determine an angle from the 1-D signals. Both sections provide customer-accessible trim registers for end-of-line calibrations.

## 1-D Signal Path

### FACTORY CHANNEL A / CHANNEL B INPUT SELECTION

Selects the input to Channel A and Channel B. This is programmed at factory level. Use the selection guide to determine which axes are used.

### FACTORY RANGE SELECTION

Factory range selection sets the analog pre-amplifier. The A31315 front end settings are configured for a limited field range. To determine the field range, consult the selection guide.

### CUSTOMER-CONTROLLABLE DATA PATH

Customer-trimmable registers allow for final test trimming in application. The equations in the following sections explain in detail the available customer trims.

NOTE: If customer registers are used to trim the signal path, performance parameters may not be guaranteed. The customer must take care in changing these components and assumes liability for device performance deviations that come about from the changes applied.

## Customer Trimming

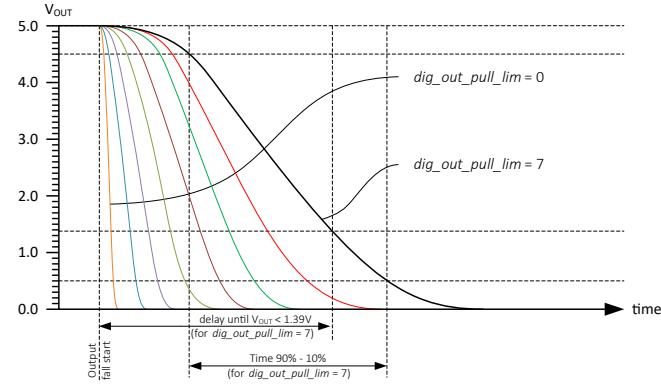

### LOW-PASS FILTER

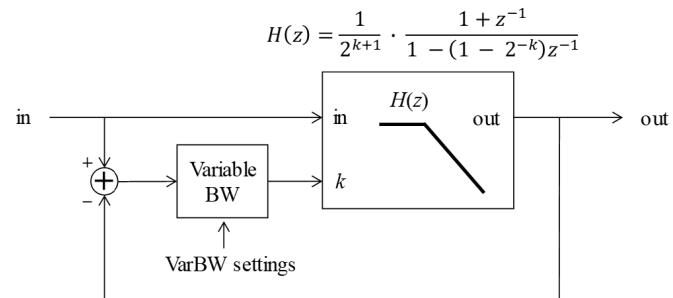

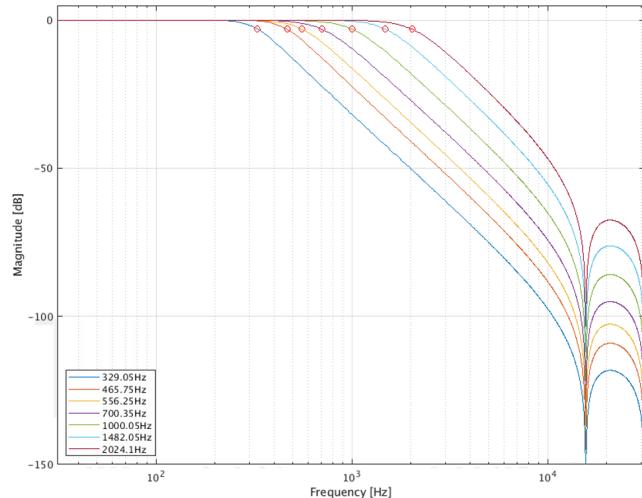

The user low-pass filter allows noise reduction without data update rate change using a combination of a CIC and IIR filter. The IIR filter is a third-order low-pass filter. The input of this filter is noted in Figure 4 above as CA0 for Channel A and CB0 for Channel B. Both channels are filtered at the same rate; there is no independent filter settings for each channel.

Equation 2:

$$\begin{aligned} CA_1 &= \text{LPF}(CA_0) \\ CB_1 &= \text{LPF}(CB_0) \end{aligned}$$

Figure 5: Low-Pass Filter

Table 2: Selection of Customer Low-Pass Filter, EEPROM Parameter bw\_sel

| bw_sel | 3 dB Frequency (Hz) | 90% Settling (ms) |

|--------|---------------------|-------------------|

| 0      | 329.1               | 1.666             |

| 1      | 465.8               | 1.172             |

| 2      | 556                 | 0.9925            |

| 3      | 700                 | 0.763             |

| 4      | 1000                | 0.554             |

| 5      | 1482                | 0.396             |

| 6      | 2024                | 0.249             |

| 7      | Adaptive            | 0.135             |

The adaptive filter has a selectable minimum and maximum bandwidth for increased customization. The minimum and maximum bandwidths are selected via the bw\_adapt\_min and bw\_adapt\_max registers respectively. The table below shows the corresponding bandwidths for each register. bw\_adapt\_min is by default set to code 0, and bw\_adapt\_max is by default set to code 7.

Table 3: bw\_adapt\_(min/max) Frequencies

| bw_adapt_(min/max) (LSB) | Frequency (Hz) |

|--------------------------|----------------|

| 0                        | 38.9           |

| 1                        | 77.8           |

| 2                        | 156.3          |

| 3                        | 314.8          |

| 4                        | 638.7          |

| 5                        | 1308.6         |

| 6                        | 2672.1         |

| 7                        | 4734.2         |

The overall filter response is given below.

**Figure 6: Overall IIR filter Response Depending on the Selected Bandwidth**

### SENSOR OUTPUT DURING LOW-PASS FILTER INITIALIZATION

After startup, the low-pass filter takes some time to settle. It may be undesirable for the output values to show this settling behavior. For this reason, the parameter `power_on_delay` allows suppressing the sensor output for a configurable amount of time. If desired, the time that the output is suppressed should be set to a value compatible with the filter settling time. It is the user's responsibility to do this. The value is not automatically chosen by the sensor to be compatible with the filter bandwidth setting.

For analog output, if the IIR output is suppressed in this manner the output will be forced to max value if `ana_init_sel` = 1 or to min value if `ana_init_sel` = 0.

For SENT output:

- If `sent_encoding_sel` = 1 and `sent_data_sel` = 0, 4, 7, or 15, an initialization code selected by parameter `sent_init_sel` will be transferred for the configured amount of time.

- In other cases, the data will be sent out with `SCN[0]` = 1 for the configured filter initialization time.

For PWM output, the POR error code for POR will be sent out for the time selected by `power_on_delay`. This error code is represented by the values shown in Table 34. The error may be superseded by errors of higher priority as per Table 34.

The `power_on_delay` options are given in Table 4.

**Table 4: Selection of output during low-pass filter startup, EEPROM Parameter `power_on_delay`**

| <code>power_on_delay</code> | Analog Fixed Output Duration (ms) | SENT Additional initialize / POR time (ms) | PWM POR state duration (ms) |

|-----------------------------|-----------------------------------|--------------------------------------------|-----------------------------|

| 0                           | 0.5                               | 0.5                                        | 0.5                         |

| 1                           | 1.0                               | 1.0                                        | 1.0                         |

| 2                           | 1.5                               | 1.5                                        | 1.5                         |

| 3                           | 2.0                               | 2.0                                        | 2.0                         |

| 4                           | 2.5                               | 2.5                                        | 2.5                         |

| 5                           | 3.0                               | 3.0                                        | 3.0                         |

| 6                           | 4.0                               | 4.0                                        | 4.0                         |

| 7                           | 0.25                              | none                                       | 0.25                        |

### FACTORY CORRECTION

The A31315 devices are factory-trimmed for the channels and field ranges noted in the selection guide. The trim provides a flat TC to all parameters and accuracy to the DS specifications for channel and angle.

Equation 3:

$$CA_2 = \text{Factory}_{\text{Correction}}(CA_1)$$

$$CB_2 = \text{Factory}_{\text{Correction}}(CB_1)$$

### ORTHOGONALITY CORRECTION

A factory-trimmed orthogonality correction is implemented. This works by modeling the orthogonality error as a cross-sensitivity from Channel A into Channel B prior to CORDIC calculation.

Equation 4:

$$CB_2' = CB_2 + \text{Phase}_{\text{Corr}} \times CA_2$$

For information on how to adapt the orthogonality correction, contact Allegro Microsystems.

**POLARITY, OFFSET, SENSITIVITY,

AND TEMPERATURE CALIBRATION**

Polarity bits are provided for each channel to invert the direction of sensitivity of either or both axes. Polarity change is the first operation performed in the customer trim path. Because of this, it should be set first to ensure the offset programmed has the proper sign.

The offset and sensitivity parameters can be used to help provide a linear output when using the device in any off-axis orientation. The angle output will be linear for well-matched input sensing vectors. When mounting off axis, one dimension often has an offset and amplitude variation relative to the other. Using chan\_x\_offs and chan\_x\_sens registers can correct this system-level mismatch, effectively providing a simple two parameter linearization method.

The offset and sensitivity temperature compensation parameters can be used to stabilize the sensor output over temperature. First- and second-order corrections, separated per channel, and separated for temperatures above and below 25°C, are provided for post-mounting offset and gain calibration.

**POLARITY CORRECTION**

Equation 5:

$$CA_3 = \begin{cases} CA_2 & \text{for } chan\_a\_pol = 0 \\ -CA_2 & \text{for } chan\_a\_pol = 1 \end{cases}$$

$$CB_3 = \begin{cases} CB_2 & \text{for } chan\_b\_pol = 0 \\ -CB_2 & \text{for } chan\_b\_pol = 1 \end{cases}$$

**SENSITIVITY ADJUSTMENT**

Equation 6:

$$CA_4 = CA_3 \times chan\_a\_sens$$

$$CB_4 = CB_3 \times chan\_b\_sens$$

The range for “chan\_x\_sens” is [0 ... 7.9995], with a resolution of  $2^{-11} = 4.88e-04$ . The default value is 2048, resulting in a gain of 1.

**SENSITIVITY CORRECTION OVER TEMPERATURE**

Equation 7:

$$CA_5 = \begin{cases} CA_4 \times (1 + chan\_a\_sens\_tc1\_cold \times (T_0 - 25^\circ C) + chan\_a\_sens\_tc2\_cold \times (T_0 - 25^\circ C)^2) & \text{Temperature} < 25^\circ C \\ CA_4 \times (1 + chan\_a\_sens\_tc1\_hot \times (T_0 - 25^\circ C) + chan\_a\_sens\_tc2\_hot \times (T_0 - 25^\circ C)^2) & \text{Temperature} \geq 25^\circ C \end{cases}$$

$$CB_5 = \begin{cases} CB_4 \times (1 + chan\_b\_sens\_tc1\_cold \times (T_0 - 25^\circ C) + chan\_b\_sens\_tc2\_cold \times (T_0 - 25^\circ C)^2) & \text{Temperature} < 25^\circ C \\ CB_4 \times (1 + chan\_b\_sens\_tc1\_hot \times (T_0 - 25^\circ C) + chan\_b\_sens\_tc2\_hot \times (T_0 - 25^\circ C)^2) & \text{Temperature} \geq 25^\circ C \end{cases}$$

The range for chan\_x\_sens\_tc1\_cold is  $[-2^{-7} \dots (2^{-7} - 2^{-17})] = -0.0078 \dots +0.0078$  with a resolution of  $2^{-17} = 7.63e-06$ .

The range for chan\_x\_sens\_tc1\_hot is  $[-2^{-8} \dots (2^{-8} - 2^{-18})] = -0.0039 \dots +0.0039$  with a resolution of  $2^{-18} = 3.81e-06$ .

The range for chan\_x\_sens\_tc2\_cold is  $[-2^{-16} \dots (2^{-16} - 2^{-25})] = -1.53e-05 \dots +1.52e-05$  with a resolution of  $2^{-25} = 2.98e-08$ .

The range for chan\_x\_sens\_tc2\_hot is  $[-2^{-14} \dots (2^{-14} - 2^{-23})] = -6.10e-05 \dots +6.09e-05$  with a resolution of  $2^{-23} = 1.19e-07$ .

**CUSTOMER OFFSET CORRECTION**

Equation 8:

$$CA_6 = CA_5 + chan\_a\_offs$$

$$CB_6 = CB_5 + chan\_b\_offs$$

The range for chan\_b\_offs is  $-32768 \dots +32764$  LSB with a resolution of 4 LSB.

**CUSTOMER OFFSET CORRECTION OVER TEMPERATURE**

Equation 9:

$$CA_7 = \begin{cases} CA_6 + chan\_a\_offs\_tc1\_cold \times (T_0 - 25^\circ C) & \text{Temperature} < 25^\circ C \\ CA_6 + chan\_a\_offs\_tc1\_hot \times (T_0 - 25^\circ C) & \text{Temperature} \geq 25^\circ C \end{cases}$$

$$CB_7 = \begin{cases} CB_6 + chan\_b\_offs\_tc1\_cold \times (T_0 - 25^\circ C) & \text{Temperature} < 25^\circ C \\ CB_6 + chan\_b\_offs\_tc1\_hot \times (T_0 - 25^\circ C) & \text{Temperature} \geq 25^\circ C \end{cases}$$

The range for chan\_x\_offs\_tc1\_cold is  $[-256 \dots +255.875]$  LSB/K with a resolution of  $2^{-3} = 0.125$  LSB/K

The range for chan\_x\_offs\_tc1\_hot is  $[-128 \dots +127.9375]$  LSB/K with a resolution of  $2^{-4} = 0.0625$  LSB/K

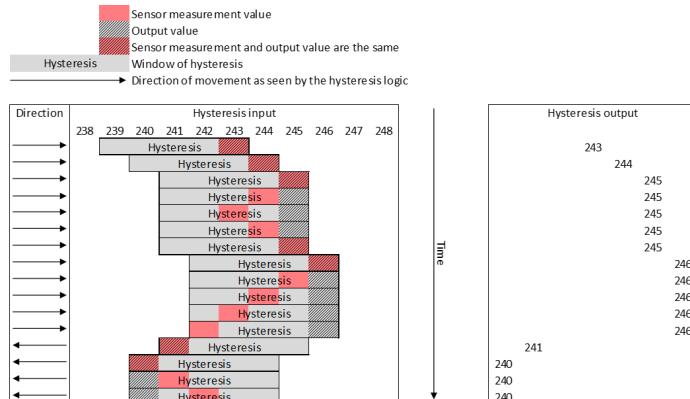

## HYSTERESIS FILTER

Equation 10:

$$CA_8 = \text{Hysteresis\_filter}(CA_7)$$

$$CB_8 = \text{Hysteresis\_filter}(CB_7)$$

The hysteresis block limits change in the sensor output to remove noise from the channels. The hysteresis block can be disabled by setting the hysteresis window width to zero. The hysteresis block input as measured by the sensor is at the “head” of the hysteresis window. As long as the hysteresis input ( $CA_7 / CB_7$ ) advances in the same direction of rotation, the hysteresis output ( $CA_8 / CB_8$ ) will be unchanged, minimizing latency. If the hysteresis input ( $CA_7 / CB_7$ ) reverses direction, the hysteresis output is held static until the input data exits the hysteresis window in either direction. If the exit is in the opposite direction of movement as to where the “head” was, the head flips to the opposite end of the hysteresis window and that becomes the new reference direction. On sensor reset, the first value change is accepted as initial direction. The behavior of the hysteresis block is shown in Figure 7.

Figure 7: Input and Output Example of Hysteresis Block

The range for  $\text{chan}_x\text{.hyst}$  is  $[0 \dots 1023]$  LSB with a resolution of 1 LSB.

## DIRECT OUTPUT REGISTER

The Channel A and Channel B data can be read directly through the digital interface for customer trimming and in-application debugging purposes.

Equation 11:

$$\text{chan\_a\_16b}[15:0] = CA_8$$

$$\text{chan\_b\_16b}[15:0] = CB_8$$

## ATAN INPUT SELECTION

In order to provide the angle output from the 3D Hall elements, the two-input function “atan2” is used. It is internally implemented using the CORDIC algorithm. The sine and cosine inputs to the ATAN2 are user-selectable based on the EEPROM parameter  $\text{cordic\_sel}$ . The CORDIC algorithm will calculate the arctangent to provide the angle between the two input vectors. This angle is related to the linear position in slide-by long stroke applications. A bypass option is provided to route channel A or channel B directly to the next processing steps. This allows using the A31315 as a 1-D sensor. When bypassing the ATAN2 calculation, the most negative 1-D value (-32768) becomes an angle of  $0^\circ$  (value 0), a zero value of the 1-D channel becomes  $180^\circ$  (value 32768), and the most positive value of the 1-D channel becomes  $359.99^\circ$  (value 65535).

Equation 12:

$$A_0 = \begin{cases} \text{atan2}(CA_8, CB_8) & \text{cordic\_bypass} = 0, \text{cordic\_chan\_order} = 0 \\ \text{atan2}(CB_8, CA_8) & \text{cordic\_bypass} = 0, \text{cordic\_chan\_order} = 1 \\ CA_8 + 32768 & \text{cordic\_bypass} = 1, \text{cordic\_chan\_order} = 0 \\ CB_8 + 32768 & \text{cordic\_bypass} = 1, \text{cordic\_chan\_order} = 1 \end{cases}$$

Note: in the equation above,  $\text{atan2}(0,1) = 0^\circ$ ,  $\text{atan2}(1,0) = +90^\circ$ ,  $\text{atan2}(0,-1) = +180^\circ$ , and  $\text{atan2}(-1,0) = +270^\circ$ . This follows from the function definition of  $\theta = \text{atan2}(\sin(\theta), \cos(\theta))$ .

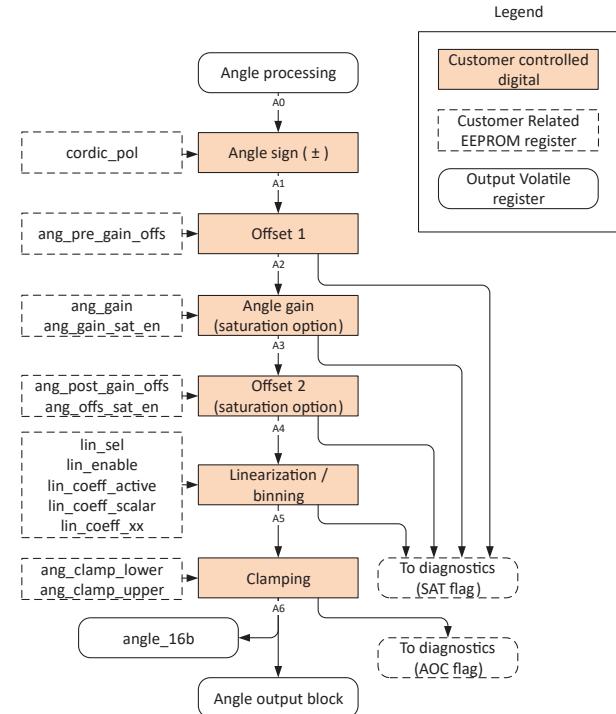

Figure 8: Angle Signal Path Processing Flow

### ANGLE SIGN (ROTATION DIRECTION)

The A31315 has a bit in EEPROM (cordic\_pol) designating the polarity of the angle reading of the device. Since angle value is calculated from the channel values, which can be polarity inverted earlier in the signal path, care must be taken to ensure the positive direction of rotation is as desired. Since each channel polarity, CORDIC input selection, and angle sign bit affects angle rotation, the equation below is provided as a quick reference for defining angle rotation.

Equation 13:

$$A_1 = \begin{cases} A_0 & \text{for } \text{cordic\_pol} = 0 \\ 360^\circ - A_0 & \text{for } \text{cordic\_pol} = 1 \end{cases}$$

### PRE-GAIN ANGLE OFFSET CORRECTION

The A31315 contains a programmable zero angle point allowing the electrical zero angle to be adjusted from the magnetic angle to match mechanical orientations. This is provided in the form of an angle offset correction at the output of the CORDIC angle calculation. This offset is a full-scale offset with a range of 0 to 360 degrees following Equation 14.

Equation 14:

$$A_2 = \text{mod}(A_1 + \text{ang\_pre\_gain\_offs}, 360^\circ)$$

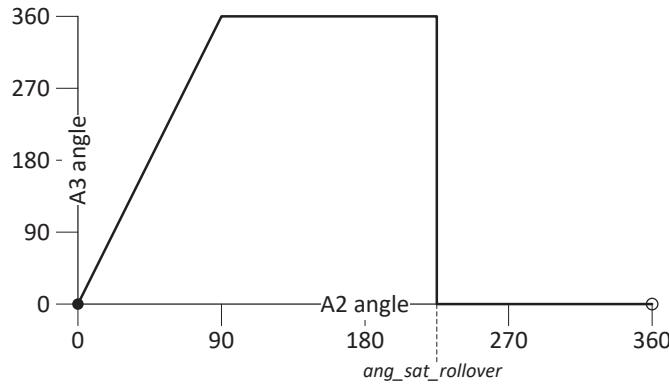

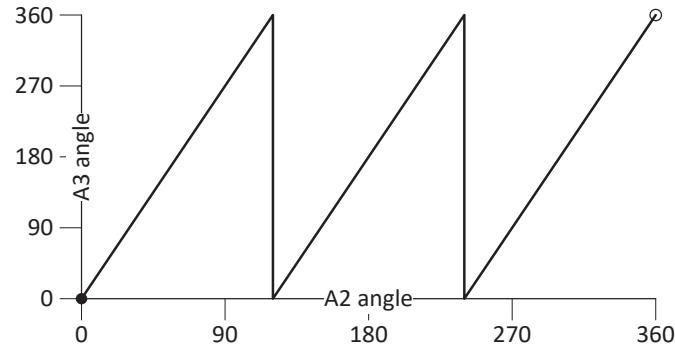

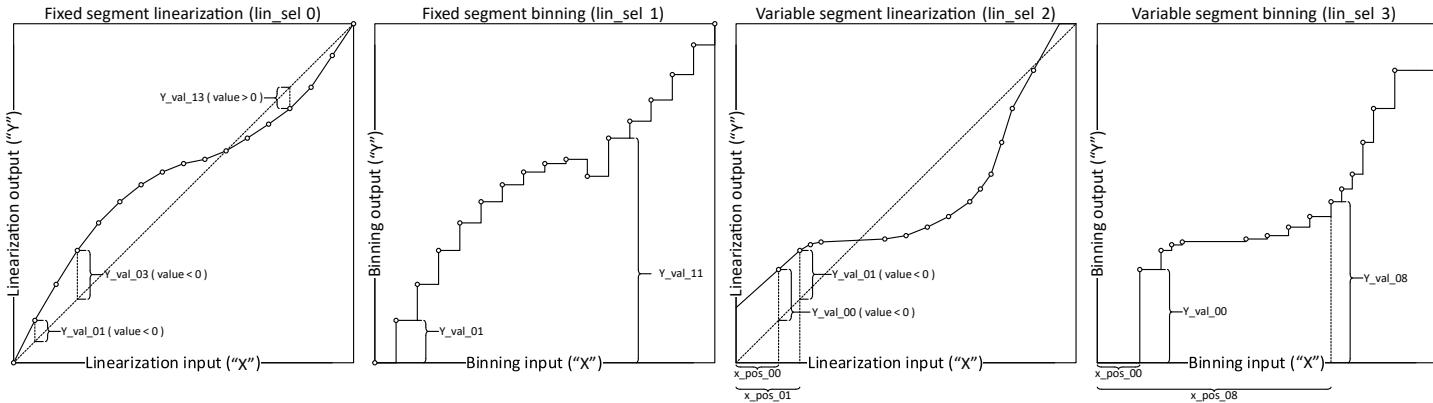

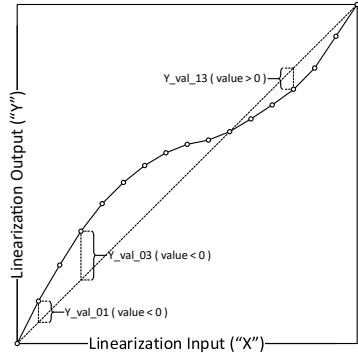

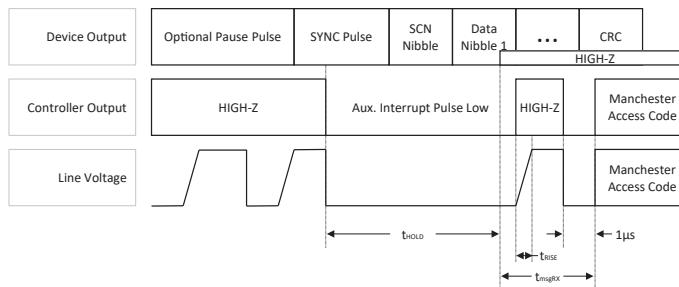

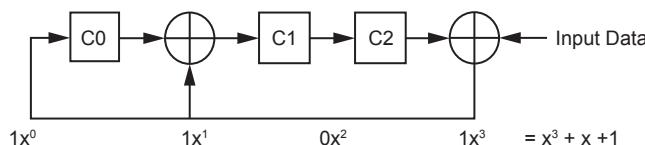

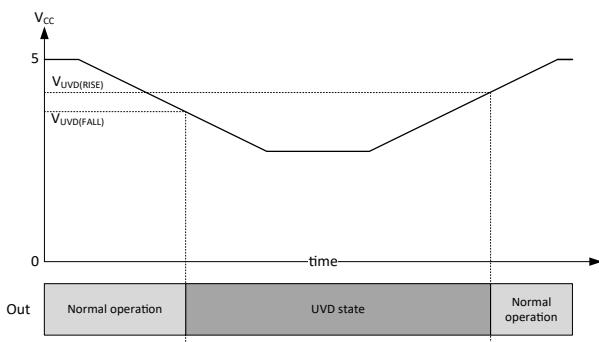

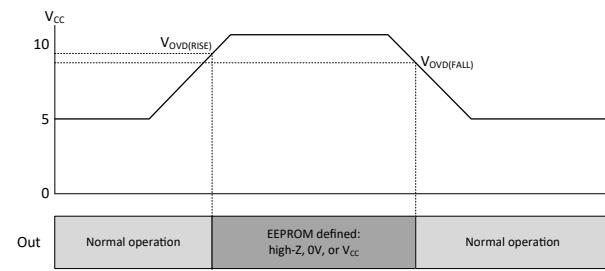

The output of the pre-gain offset correction block,  $A_2$  is always allowed to roll over from maximum output to minimum output as needed. It is possible to compare the output angle of this block to programmed limits using the parameters  $\text{ang\_thresh\_low}$  and  $\text{ang\_thresh\_high}$ , if  $\text{ang\_thresh\_en} = 1$ . These limits do not saturate the  $A_2$  angle but can only be used to cause a saturation flag.