# Buck Regulator -Integrated, Synchronous, Light Load Efficiency

# 2.0 A, 1.0 MHz

NCP5252 is a synchronous buck regulator with integrated high-side and low-side MOSFETs. The device is capable of operating from a 5 V or 12 V supply and can output a voltage down to 0.6 V. The switching frequency is adjustable from 333 kHz up to 1.0 MHz and has the ability to provide skip mode for light load efficiency. NCP5252 protection features include Under Voltage Lock Out (UVLO), Over Voltage Protection (OVP), Cycle-by-Cycle Current Protection (OCP) and Thermal Shutdown. The part is packaged in a 3x3 mm QFN-16.

#### **Features**

- 1% Accuracy 0.6 V Reference

- V<sub>CC</sub> Voltage 4.5 V to 13.2 V

- Adjustable Output Voltage Range: 0.6 V to 5.0 V

- Transient Response Enhancement (TRE) Feature.

- Low Side Lossless Sense Current Control

- Input Voltage Feed Forward Control

- Internal Digital Soft-Start

- Integrated Output Discharge (Soft-Stop)

- Cycle-by-Cycle Current Limit

- Power Good Indication

- Overvoltage and Undervoltage Protection

- Thermal Shutdown Protection

- Power Saving Mode at Light Load

- Integrated Boost Diode

- QFN-16 (3 mm x 3 mm)

- These Devices are Pb-Free and are RoHS Compliant

#### **Typical Applications**

- Desktop Application

- System Power

- XDSL, Modems, DC-DC Modules

- Set Top Box

- HD Driver

- LED Driver, DVD Recorders

### ON Semiconductor®

http://onsemi.com

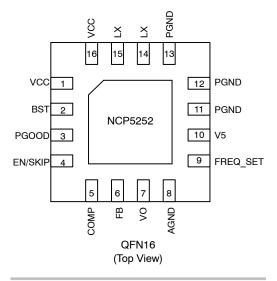

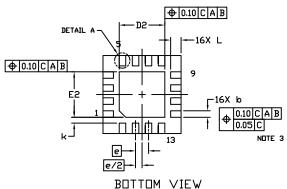

QFN16 CASE 485G

# MARKING DIAGRAM

16 O N5252 ALYW•

A = Assembly Location

L = Wafer Lot Y = Year W = Work Week • Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

| Device       | Package            | Shipping <sup>†</sup> |

|--------------|--------------------|-----------------------|

| NCP5252MNTXG | QFN16<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

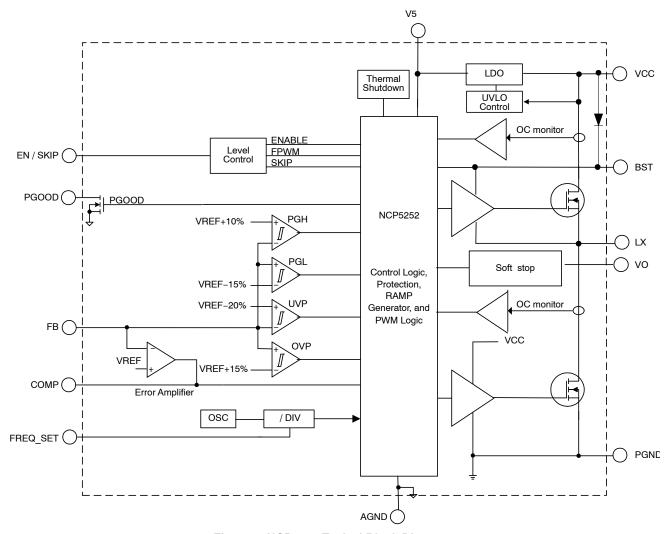

Figure 1. NCP5252 Typical Block Diagram

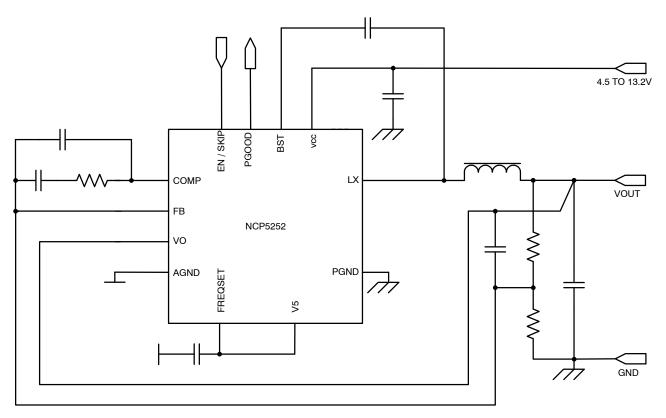

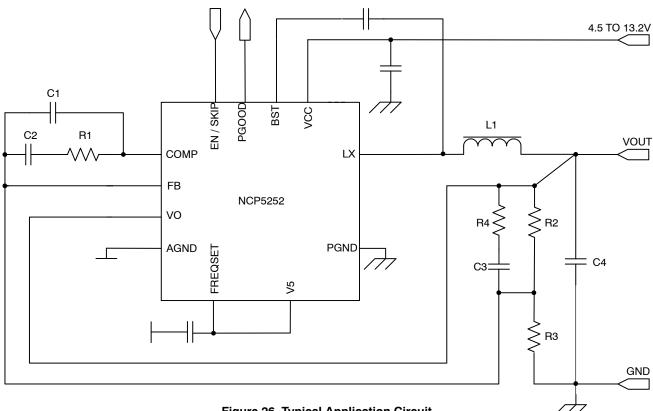

Figure 2. NCP5252 Typical Application Circuits

# PIN FUNCTION DESCRIPTION

| Pin No | Symbol          | Description                                                                                                                                                                                                                                                   |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | V <sub>CC</sub> | Internal LDO power supply                                                                                                                                                                                                                                     |

| 2      | BST             | Top MOSFET driver input supply, place a ceramic capacitor between LX and BST.                                                                                                                                                                                 |

| 3      | PGOOD           | Output voltage power good indication. The power good pin is an open drain indication flag. The PGOOD pin is low impedance if the output voltage is outside the comparator window and is high impedance if the output voltage is inside the comparator window. |

| 4      | EN/SKIP         | The enable pin is used to enable the part and also set skip mode or forced PWM.                                                                                                                                                                               |

| 5      | COMP            | Output of the error amplifier                                                                                                                                                                                                                                 |

| 6      | FB              | Output voltage feedback                                                                                                                                                                                                                                       |

| 7      | VO              | Output voltage monitor                                                                                                                                                                                                                                        |

| 8      | AGND            | Analog ground                                                                                                                                                                                                                                                 |

| 9      | FREQ_SET        | Frequency selection pin, 0 V = 333k, No connect = 500 kHz, 5 V = 1.0 MHz                                                                                                                                                                                      |

| 10     | V5              | Output to the internal power supply for the analog circuitry                                                                                                                                                                                                  |

| 11–13  | PGND            | Ground reference and high-current return path for the bottom power MOSFET.                                                                                                                                                                                    |

| 14–15  | LX              | Switch node between the top MOSFET and bottom MOSFET.                                                                                                                                                                                                         |

| 16     | V <sub>CC</sub> | High Side MOSFET input voltage connection                                                                                                                                                                                                                     |

| 17     | EPAD            | Connect to PGND for thermal enhancement. Exposed pad is not electrically connected.                                                                                                                                                                           |

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                          | Symbol                             | Value                                      | Unit |

|-------------------------------------------------|------------------------------------|--------------------------------------------|------|

| V <sub>CC</sub> Power Supply Voltage to AGND    | V <sub>CC</sub>                    | -0.3, 15                                   | V    |

| EN / SKIP to AGND                               | V <sub>EN</sub>                    | -0.3, 6                                    | V    |

| Bootstrap Supply Voltage: BST to LX             | V <sub>BST</sub> – V <sub>LX</sub> | -0.3, 15                                   | V    |

| LDO regulator: V5 to AGND                       | V5 – V <sub>AGND</sub>             | -0.3, 6                                    | V    |

| Input / Output Pins to AGND                     | V <sub>IO</sub>                    | -0.3, 6                                    | V    |

| Switch Node to PGND                             | V <sub>LX</sub>                    | 15<br>20 (50 ns)<br>-1 (DC)<br>-5 (200 ns) | V    |

| PGND                                            | $V_{PGND}$                         | -0.3, 0.3                                  | V    |

| Thermal Resistance Junction-to-Ambient (0 lfpm) | $R_{	hetaJA}$                      | 90                                         | °C/W |

| Thermal Resistance Junction-to-Case (0 lfpm)    | $R_{	heta JC}$                     | 15                                         | °C/W |

| Operating Ambient Temperature Range             | T <sub>A</sub>                     | -40 to + 85                                | °C   |

| Operating Junction Temperature Range            | T <sub>J</sub>                     | -40 to + 150                               | °C   |

| Storage Temperature Range                       | T <sub>stg</sub>                   | -55 to +150                                | °C   |

| Power Dissipation                               | P <sub>D</sub>                     | 1.4                                        | W    |

| Moisture Sensitivity Level                      | MSL                                | 1                                          | -    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

### **V<sub>CC</sub> UNDERVOLTAGE**

| Parameter                           | Test Conditions | Min | Тур | Max | Unit |

|-------------------------------------|-----------------|-----|-----|-----|------|

| V <sub>CC</sub> UVLO Rise Threshold |                 | 4.1 | 4.3 | 4.5 | V    |

| V <sub>CC</sub> UVLO Hysteresis     |                 | 300 | 400 | 500 | mV   |

# **ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ = 4.5 to 13.2 V, $T_A$ = -40°C to 85°C, unless other noted)

| Characteristics                                 | Symbol                | Test Conditions                                                             | Min            | Тур        | Max            | Unit |

|-------------------------------------------------|-----------------------|-----------------------------------------------------------------------------|----------------|------------|----------------|------|

| SUPPLY VOLTAGE                                  |                       |                                                                             |                |            |                |      |

| Input Voltage                                   | V <sub>CC</sub>       |                                                                             | 4.5            |            | 13.2           | V    |

| POR Threshold for Internal Reset<br>Logic       | V <sub>CC_POR</sub>   |                                                                             |                | 3.0        | 3.7            | V    |

| SUPPLY CURRENT                                  |                       |                                                                             |                |            | •              |      |

| V <sub>CC</sub> Quiescent Supply Current        | I <sub>CC_FPWM</sub>  | EN/SKIP = 5 V, $V_{FB}$ = 1 V (No switching),<br>$V_{CC}$ = 4.5 V to 13.2 V |                | 1.0        | 2.5            | mA   |

| V <sub>CC</sub> Shutdown Current                | I <sub>VCC_SD</sub>   | EN/SKIP = 0 V                                                               |                |            | 10             | μΑ   |

| BST Quiescent Supply Current                    | I <sub>BST_FPWM</sub> | EN/SKIP = H, V <sub>FB</sub> = 1 V, V <sub>BST</sub> = 5 V                  |                |            | 0.3            | mA   |

| BST Shut Down Current                           | I <sub>BST_SD</sub>   | EN/SKIP = L, V <sub>FB</sub> = 1 V, V <sub>BST</sub> = 5 V                  |                |            | 10             | μΑ   |

| VCC Input Current                               | IV <sub>CC</sub>      | FREQ_SET = AGND. FREQ = 333 kHz                                             |                | 18         |                | mA   |

| LDO REGULATOR                                   |                       |                                                                             |                |            | •              |      |

| V5 Regulator Voltage                            | V5                    | $V_{CC} > 6 \text{ V}, I_{V5} = 5 \text{ mA}$                               | 4.85           | 5.0        | 5.15           | V    |

| V5 Rise Threshold                               | V5_th+                | Wake Up                                                                     | 4.1            | 4.3        | 4.45           | V    |

| V5 UVLO Hysteresis                              | V5 <sub>HYS</sub>     |                                                                             | 300            | 400        | 500            | mV   |

| V5 Loading                                      | V5 <sub>LOAD</sub>    |                                                                             |                |            | 3.0            | mA   |

| V5 Current Limit                                | I <sub>LIMIT_V5</sub> |                                                                             | 20             |            |                | mA   |

| Drop-out Voltage (V <sub>CC</sub> - V5)         | $V_{DR}$              | Io = 5 mA, T <sub>A</sub> = 25°C, V <sub>CC</sub> = 4.5 V, FB = 1V          |                |            | 200            | mV   |

| POWER GOOD                                      |                       |                                                                             |                |            | •              |      |

| Power Good High Threshold                       | VPGH                  | PGOOD in from higher Vo<br>(PGOOD goes high)                                | 100            | 110        | 120            | %    |

| Power Good High Hysteresis                      | VPGH_HYS              | PGOOD high hysteresis<br>(PGOOD goes low)                                   |                | 5          |                | %    |

| Power Good Low Threshold                        | VPGL                  | PGOOD in from lower Vo<br>(PGOOD goes high)                                 | 75             | 85         | 95             | %    |

| Power Good Low Hysteresis                       | VPGL_HYS              | PGOOD low hysteresis<br>(PGOOD goes low)                                    |                | -5         |                | %    |

| Power Good High Delay                           | Td_PGH                |                                                                             |                | 150        |                | μs   |

| Power Good Low Delay                            | Td_PGL                |                                                                             |                | 1.5        |                | μs   |

| Output Overvoltage Rising<br>Threshold          | OVPth+                | OVPth+ = VPGH + VPGH_SYS                                                    | 105            | 115        | 125            | %    |

| Over voltage Fault Propagation<br>Delay         | OVPTblk               | FB Forced 2% above trip threshold                                           |                | 1.5        |                | μs   |

| Output Undervoltage Trip<br>Threshold           | UVPth                 | UVPth = VPGL + VPGL_HYS                                                     | 70             | 80         | 90             | %    |

| Output Undervoltage Protection<br>Blanking Time | UVPTblk               |                                                                             |                | 8.0        |                | μs   |

| REFERENCE OUTPUT                                |                       |                                                                             |                |            |                |      |

| Internal Reference Voltage                      | V <sub>REF</sub>      | 25°C<br>-40°C to 85°C                                                       | 0.594<br>0.591 | 0.6<br>0.6 | 0.606<br>0.609 | V    |

| Output Voltage Accuracy (Note 1)                |                       | V <sub>IN</sub> = 12 V, Io = 0 A to 2 A                                     | -1             | 0          | +1             | %    |

| Line Regulation (Note 1)                        |                       | V <sub>IN</sub> = 5 to 12 V, I <sub>OUT</sub> = 500 mA                      |                | 0.1        |                | %/V  |

| OSCILLATOR                                      | -                     |                                                                             |                | -          | -              | -    |

| Operation Frequency                             | F <sub>SW</sub>       | FREQ_SET = V5                                                               | 900            | 1000       | 1100           | kHz  |

| -                                               |                       | FREQ_SET = NC                                                               | 450            | 500        | 550            | kHz  |

|                                                 |                       | FREQ_SET = AGND                                                             | 300            | 333        | 366            | kHz  |

| INTERNAL SOFT-START                             | -                     |                                                                             |                | -          | -              | -    |

| Soft-Start Time                                 | t <sub>SS</sub>       | Digital Soft–Start (V <sub>OUT</sub> from 10% to 90%)                       |                | 800        | <u> </u>       | μS   |

| 1 Guaranteed by design, not tested              |                       | . 35. ,                                                                     |                |            | -              |      |

<sup>1.</sup> Guaranteed by design, not tested in production. 2. Test mode disables the  $T_{\rm on}/T_{\rm off}$  min.

# **ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ = 4.5 to 13.2 V, $T_A$ = -40°C to 85°C, unless other noted)

| Characteristics                                        | Symbol                  | Test Conditions                                                                                    | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------|------|------|------|------|

| SWITCHING MODULATOR                                    |                         |                                                                                                    |      |      |      |      |

| Minimum T <sub>on</sub>                                | T <sub>on_min</sub>     | (Note 1)                                                                                           | 40   | 50   | 60   | ns   |

| Minimum T <sub>off</sub>                               | T <sub>off_min</sub>    | (Note 1)                                                                                           | 200  | 225  | 250  | ns   |

| PWM Comparator Offset                                  |                         | (Note 1)                                                                                           |      | 5.0  | 10   | mV   |

| Propagation Delay of PWM<br>Comparator                 | TD_PWM                  | (Note 1)                                                                                           |      |      | 20   | ns   |

| VOLTAGE ERROR AMPLIFIER                                |                         |                                                                                                    |      |      |      |      |

| DC Gain                                                | GAIN_VEA                | (Note 1)                                                                                           | 80   | 88   |      | dB   |

| Open-Loop Phase Margin                                 | PH_EA                   | (Note 1)                                                                                           | 50   |      |      | Deg  |

| Unity Gain Bandwidth                                   | BW_VEA                  | (Note 1)                                                                                           | 15   | 20   |      | MHz  |

| Slew Rate                                              | SR_VEA                  | COMP PIN TO GND = 100 pF<br>(Note 1)                                                               | 5.0  |      |      | V/μs |

| FB Bias Current                                        | I <sub>bias_FB</sub>    |                                                                                                    |      |      | 0.1  | μΑ   |

| Output Voltage Swing                                   | V <sub>max_EA</sub>     | I <sub>source_EA</sub> = 2mA                                                                       | 3.3  | 3.5  |      | V    |

|                                                        | V <sub>min_EA</sub>     | I <sub>sink_EA</sub> = 2mA                                                                         |      | 0.15 | 0.3  | V    |

| OVERCURRENT PROTECTION LIN                             |                         |                                                                                                    |      |      |      |      |

| High Side Peak Current Limit (Cycle-by-Cycle)          | HSOC                    | T <sub>on</sub> Minimum > 100 ns<br>(Notes 1 & 2)                                                  | 3.4  | 4.0  | 4.6  | Α    |

| Low Side Valley Current Limit,<br>Short-Circuit (4 μs) | LSOC_S                  | (Notes 1 & 2)                                                                                      | 3.0  | 3.75 | 4.5  | Α    |

| Low Side Valley Current Limit (Current Limit, 16 μs)   | LSOC_L                  | (Notes 1 & 2)                                                                                      | 2.0  | 2.5  | 3.4  | Α    |

| POWER OUTPUT SECTION                                   |                         |                                                                                                    | •    |      |      |      |

| Internal Main FET ON-Resistance                        | R <sub>DS(on)_M</sub>   | $(I_{LX}=100 \text{mA}, VBST-LX = 5 \text{ V}, FB = 0, T_A = 25^{\circ}\text{C}) \text{ (Note 1)}$ |      | 150  | 225  | mΩ   |

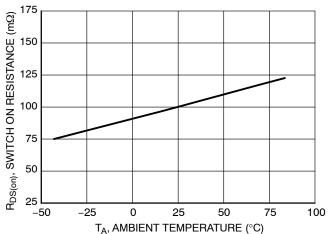

| Internal Sync FET ON-Resistance                        | R <sub>DS(on)_F</sub>   | (I <sub>LX</sub> = 100 mA, FB = 1 V, T <sub>A</sub> = 25°C)<br>(Note 1)                            |      | 100  | 150  | mΩ   |

| LX Leakage Current                                     | LX_LK                   | V <sub>EN</sub> = 0V, LX = 0, V <sub>CC</sub> = 13.2 V                                             |      |      | +5.0 | μΑ   |

|                                                        |                         | LX = 13.2, V <sub>CC</sub> = 13.2 V                                                                |      |      | -5.0 | μΑ   |

| CONTROL SECTION                                        |                         |                                                                                                    |      |      |      |      |

| EN / SKIP Logic Input Voltage for                      | V <sub>EN_DISABLE</sub> | Set as Disable                                                                                     | 0.7  | 1.0  | 1.3  | V    |

| Disable                                                | V <sub>EN_HYS</sub>     | Hysteresis                                                                                         |      | 300  |      | mV   |

| EN / SKIP Logic Input Voltage for FPWM                 | V <sub>EN_FPWM</sub>    | Set as FCCM mode                                                                                   | 1.7  | 1.95 | 2.10 | V    |

| EN / SKIP Logic Input Voltage for                      | V <sub>EN_SKIP</sub>    | Set as SKIP Mode                                                                                   | 2.25 | 2.45 | 2.65 | V    |

| Skip Mode                                              | V <sub>EN_HYS</sub>     | Hysteresis                                                                                         |      | 250  |      | mV   |

| EN / SKIP Source Current                               | I <sub>EN</sub> SOURCE  | V <sub>EN SKIP</sub> = 0 V                                                                         |      |      | 0.1  | μА   |

| EN / SKIP Sink Current                                 | I <sub>EN_SINK</sub>    | V <sub>EN_SKIP</sub> = 5 V                                                                         |      |      | 0.1  | μА   |

| EN_SKIP Logic Input Delay                              |                         | Change mode delay active                                                                           |      | 3    |      | Clk  |

| PGOOD Pin ON Resistance                                | PGOOD_R                 | I_PGOOD = 5 mA                                                                                     |      | 75   |      | Ω    |

| PGOOD Pin OFF Current                                  | PGOOD_LK                | PGOOD = 5 V                                                                                        |      |      | 1    | μΑ   |

| OUTPUT DISCHARGE MODE                                  |                         |                                                                                                    |      |      |      |      |

| Output Discharge On-Resistance                         | R <sub>discharge</sub>  | EN = 0 V                                                                                           |      | 20   | 35   | Ω    |

| THERMAL SHUTDOWN                                       | 9-                      |                                                                                                    | •    |      |      |      |

| Thermal Shutdown                                       | T <sub>sd</sub>         | (Note 1)                                                                                           |      | 150  |      | °C   |

| Thermal Shutdown Hysteresis                            | T <sub>sdhys</sub>      | (Note 1)                                                                                           |      | 25   |      | °C   |

|                                                        | Sanyo                   | · '                                                                                                |      |      |      |      |

<sup>1.</sup> Guaranteed by design, not tested in production. 2. Test mode disables the  $T_{\rm on}/T_{\rm off}$  min.

#### **TYPICAL OPERATING CHARACTERISTICS**

Figure 3. Sync FET ON Resistance vs. Temperature

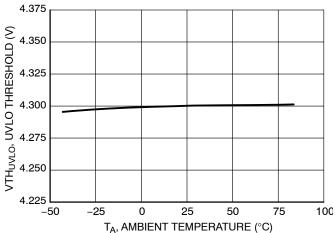

Figure 4. UVLO Threshold vs. Temperature

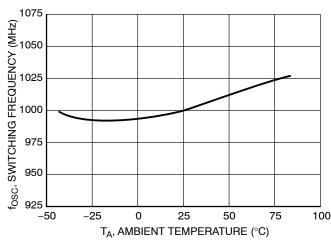

Figure 5. Switching Frequency vs.

Temperature

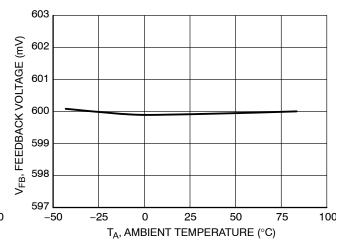

Figure 6. Feedback Input Threshold vs.

Temperature

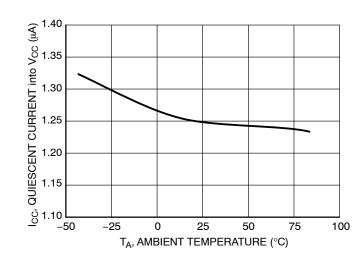

Figure 7. Quiescent Current into  $V_{CC}$  vs. Temperature

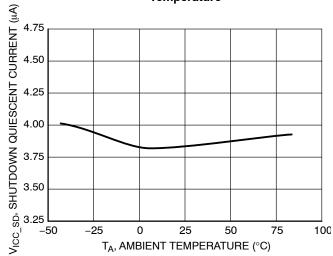

Figure 8. Shutdown Quiescent Current vs. Temperature

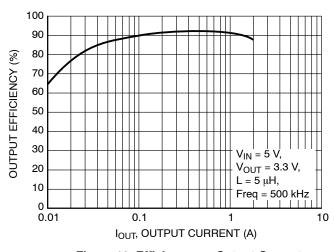

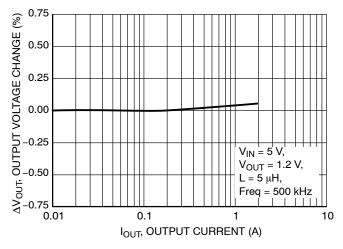

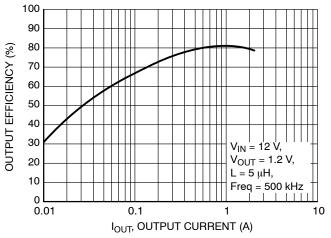

#### TYPICAL OPERATING CHARACTERISTICS

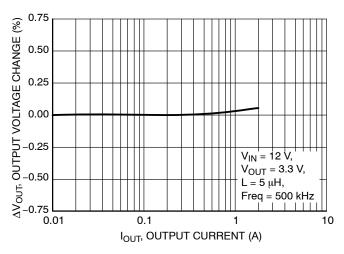

Figure 9. Output Voltage Change vs. Output Current

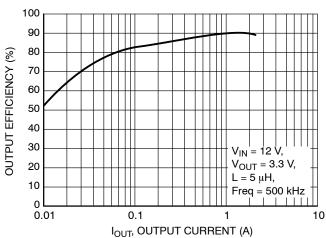

Figure 10. Efficiency vs. Output Current

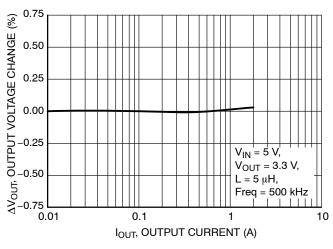

Figure 11. Output Voltage Change vs. Output

Current

Figure 12. Efficiency vs. Output Current

Figure 13. Output Voltage Change vs. Output Current

Figure 14. Efficiency vs. Output Current

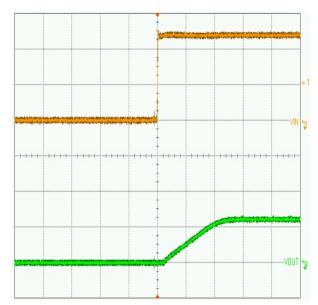

$\begin{aligned} &(\text{Vin} = 12 \text{ V}, \text{ I}_{LOAD} = 10 \text{ mA}, \\ &L = 5 \text{ } \mu\text{H}, \text{C}_{OUT} = 100 \text{ } \mu\text{F}) \\ &\text{Upper trace: Input voltage, 5 V/div} \\ &\text{Lower trace: Output voltage, 1 V/div} \end{aligned}$

Time base: 500  $\mu s/div$

Figure 15. Soft–Start Waveforms for  $V_{out}$  = 3.3 V

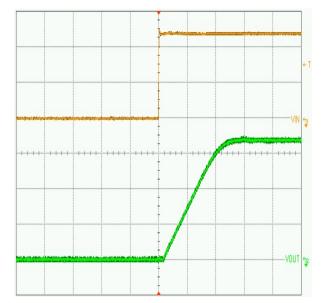

$\begin{aligned} & \text{(Vin = 12 V, I}_{LOAD} = 10 \text{ mA,} \\ & \text{L = 5 } \mu\text{H,C}_{OUT} = 100 \text{ }\mu\text{F)} \\ & \text{Upper trace: Input voltage, 5 V/div} \\ & \text{Lower trace: Output voltage, 1 V/div} \end{aligned}$

Time base: 500  $\mu s/div$

Figure 16. Soft–Start Waveforms for  $V_{out}$  = 1.2 V

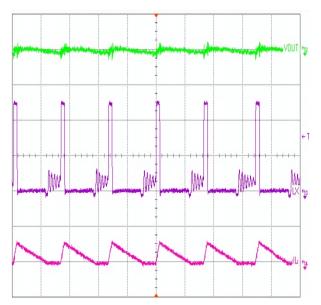

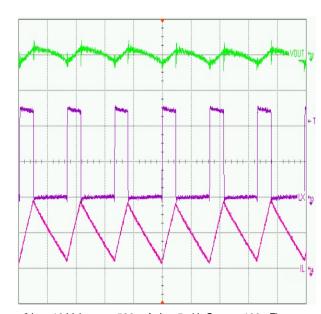

$(V_{in}=12~V,~I_{LOAD}=200~mA,~L=5~\mu H,~C_{OUT}=100~\mu F)$  Upper trace: Output ripple voltage, 50 mV/div Middle trace: Lx pin switching waveform, 5 V/div Lower trace: Inductor current waveforms, 1 A/div

Time base: 2 µs/div

Figure 17. DCM Switching Waveforms for Vout = 1.2 V

$(V_{in}=12~V,~I_{LOAD}=200~mA,~L=5~\mu H,~C_{OUT}=100~\mu F)$  Upper trace: Output ripple voltage, 50 mV/div Middle trace: Lx pin switching waveform, 5 V/div Lower trace: Inductor current waveforms, 500 mA/div Time base: 2  $\mu s/div$

Figure 19. DCM Switching Waveforms for  $V_{out} = 3.3 \text{ V}$

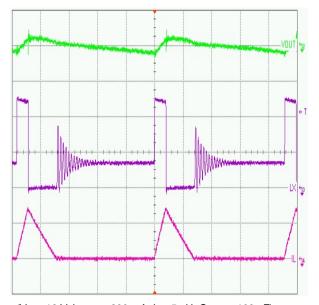

$\label{eq:continuous} \begin{array}{l} (V_{in}=12~V,~I_{LOAD}=1~A,~L=5~\mu H,~C_{OUT}=100~\mu F) \\ Upper trace:~Output~ripple~voltage,~50~mV/div\\ Middle~trace:~Lx~pin~switching~waveform,~5~V/div\\ Lower~trace:~Inductor~current~waveforms,~1~A/div\\ Time~base:~2~\mu s/div \end{array}$

Figure 18. CCM Switching Waveforms for V<sub>out</sub> = 1.2 V

$(V_{in}=12~V,~I_{LOAD}=500~mA,~L=5~\mu H,~C_{OUT}=100~\mu F)$  Upper trace: Output ripple voltage, 50 mV/div Middle trace: Lx pin switching waveform, 5 V/div Lower trace: Inductor current waveforms, 500 mA/div Time base: 2  $\mu s/div$

Figure 20. CCM Switching Waveforms for  $V_{out} = 3.3 \text{ V}$

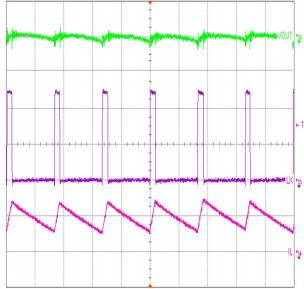

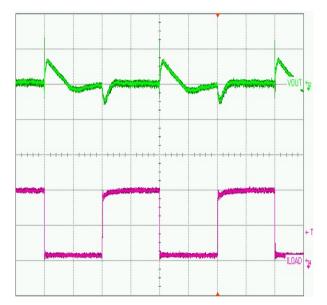

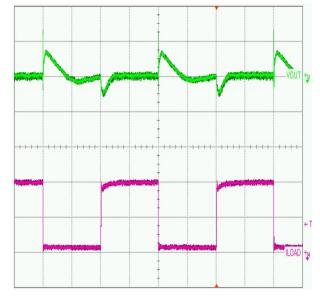

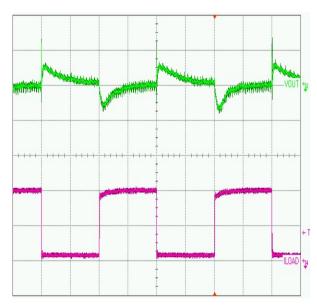

(Vin = 12 V, L = 5  $\mu$ H, C<sub>OUT</sub> = 100  $\mu$ F, Freq = 500 kHz) Upper trace: Output dynamic voltage, 100 mV/div

Lower trace: Output current, 1 A/div

Time base : 50  $\mu s/\text{div}$

Figure 21. Load Transient Response for V<sub>out</sub> = 1.2 V

(Vin = 12 V, L = 5  $\mu$ H, C<sub>OUT</sub> = 100  $\mu$ F, Freq = 1 MHz) Upper trace: Output dynamic voltage, 100 mV/div

Lower trace: Output current, 1 A/div

Time base : 50 µs/div

Figure 23. Load Transient Response for V<sub>out</sub> = 3.3 V

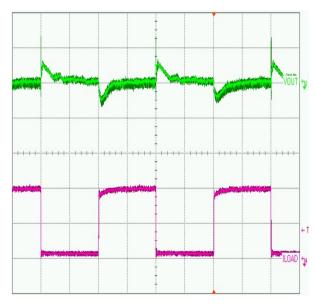

( $V_{in}$  = 5 V, L = 5  $\mu$ H,  $C_{OUT}$  = 100  $\mu$ F, Freq = 1 MHz) Upper trace: Output dynamic voltage, 100 mV/div

Lower trace: Output current, 1 A/div

Time base : 50  $\mu$ s/div

Figure 22. Load Transient Response for V<sub>out</sub> = 1.2 V

( $V_{in}$  = 5 V, L = 5  $\mu$ H,  $C_{OUT}$  = 100  $\mu$ F, Freq = 333 kHz) Upper trace: Output dynamic voltage, 100 mV/div

Lower trace: Output current, 1 A/div

Time base : 50  $\mu s/\text{div}$

Figure 24. Load Transient Response for V<sub>out</sub> = 3.3 V

#### **DETAILED OPERATING DESCRIPTION**

#### General

The NCP5252 is a PWM regulator intended for DC–DC conversion from 5 V & 12 V buses and supplies up to a 2 A load. The NCP5252 is a step down synchronous–rectifier buck topology regulator with integrated high–side and a low–side NMOS switches. The output voltage of the converter can be precisely regulated down to 600 mV  $\pm 1.0\%$  when the  $V_{FB}$  pin is tied to  $V_{OUT}$ . The switching frequency can be adjusted to 333 kHz, 500 kHz, or 1 MHz. A skip mode can be enabled to provide light load efficiency.

The NCP5252 includes the following features: power good monitor, internal soft-start, cycle-by-cycle current limit, short circuit protection, output undervoltage/overvoltage protection, and thermal shutdown.

#### **Control Logic**

During start—up the internal LDO is activated and power—on reset occurs which resets the logic and all protection faults. The device will begin its start up sequence and the functionality will be determined by the voltage at the EN/SKIP pin. When voltage of EN/SKIP is below VEN\_DISABLE, the converter will shut down. If the voltage of EN/SKIP is set between VEN\_FPWM and VEN\_SKIP, the device will be in PWM mode of operation. When the voltage level of EN/SKIP is above VEN\_SKIP, the device will operate in PFM power saving mode. Once  $V_{REF}$  reaches its regulation voltage, an internal signal will wake up the output undervoltage supply monitor which will assert a "GOOD" condition. In addition, the NCP5252 continuously monitors the  $V_{CC}$  level with an undervoltage lockout (UVLO) function.

#### Forced PWM Operation (FPWM Mode)

To place the device into force PWM mode, the EN/SKIP pin voltage should be set between VEN\_FPWM and VEN\_SKIP thresholds. During the soft-start operation, the NCP5252 will automatically run as FPWM mode until the output voltage is higher than the internal soft-start ramp.

In FPWM mode in each switching cycle, the high-side MOSFET turns on for a time period defined by the ratio of input voltage to output voltage known as duty ratio. After a short period of time following high-side MOSFET turn off, the low-side MOSFET turns on and remains on for the remainder of the switching cycle. At currents below the critical conduction point, the low-side MOSFET will sync current out of the output capacitor, reducing overall converter efficiency at light loads.

#### Pulse Skipping Operation (Skip Mode/PFM)

The device operates in skip mode if the EN/SKIP pin voltage is greater than 2.9 V. Skip mode can reduce the switching loss in light load conditions.

When the converter inductor current is greater than the critical conduction point, the converter will run in continuous-conduction-mode (CCM) which behaves exactly the same as FPWM mode. When the inductor current

crosses zero from positive to negative, the low-side MOSFET is shut off so that current is not pulled out of the output capacitor. A high-side MOSFET turn on is not initiated until the COMP voltage exceeds the bottom of the PWM ramp.

#### **Transient Response Enhancement (TRE)**

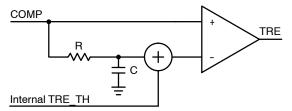

To improve transient response in CCM, a transient response enhancement circuitry is implemented inside the NCP5252.

In CCM operation, the controller continuously monitors the COMP pin voltage of the error amplifier and detects load transient events. The functional block diagram of TRE is shown as follows:

Figure 25. Block Diagram of TRE Circuit

If a large transient occurs, the COMP signal will exceed the comparator threshold indicating that a transient has occurred and action is required. When the comparator trips an extra high-side pulse is generated and the converter appears to run at a higher frequency. Once the transient has passed, the converter returns to normal operation and normal switching frequency.

#### **Voltage Feed Forward**

The NCP5252 has a voltage feed forward derived ramp. Voltage feed-forward is employed to ease loop compensation for wide-input-range designs and provide better line transient response. The ramp generator provides voltage feed-forward control by varying the PWM ramp slope with line voltage. One important thing to note is that since the slope changes with the input voltage, the ramp height will also change, resulting in an almost constant gain over input voltages. Varying the PWM ramp directly with line voltage provides excellent response to line variations, because the PWM is not required to wait for loop delays before changing the duty cycle.

The peak to peak ramp voltage can be calculated using the following equation:

$$V_{RAMP\ PP} = 0.25 \cdot V_{IN}$$

#### **Overcurrent Protection (OCP)**

The NCP5252 will protect the system if an overcurrent event occurs. The regulator will continuously monitor the output current through the internal MOSFETs. If the high-side MOSFET current exceeds the internal current limit threshold, it will be turned off. If a repetitive overcurrent event occurs, both MOSFETs will be turned off and the device will hold for 3 normal soft-start periods

before re-starting. A discharge resistor is turned on to discharge V<sub>o</sub> before re-starting.

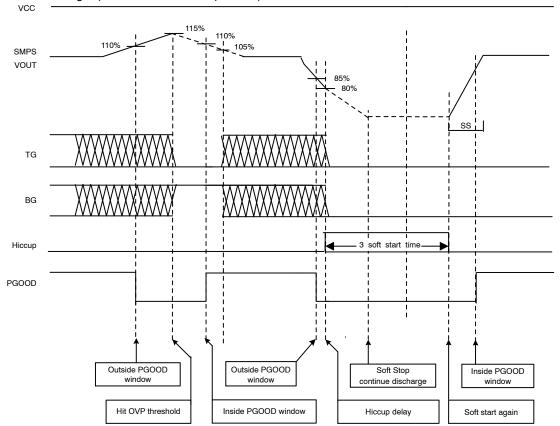

#### Overvoltage Protection (OVP)

When the SMPS output voltage is above 115% (typ) of the preset nominal regulation voltage for over 1.5 µs, an OV fault is set. The high-side MOSFET will turn off and the low-side MOSFET will be turned on to discharge the output until V<sub>0</sub> drops below the default threshold (105%). Once the output voltage is below the overvoltage window, the device will recover to normal operation.

#### **Undervoltage Protection (UVP)**

A UVP circuit monitors the output voltage to detect an undervoltage event. The undervoltage limit is 80% (typ) of the nominal output voltage level. If the output voltage is below this threshold for over 4 switching cycles, a UVP fault is set. The high-side and low-side MOSFETs are turned off and a discharge resistor is turned on to discharge the output

voltage for 3 soft-start periods. Once the 3 soft-start periods have ended, the regulator will go through a normal soft-start cycle.

### **LDO Regulator**

The internal LDO regulator (V5) can provide up to 20 mA (typ) for internal analog circuitry. Connect a capacitor to pin V5 for proper regulation.

#### **Undervoltage Logout**

The UVLO circuit will activate when the V<sub>CC</sub> voltage is below 3.5 V (typ). At that time both MOSFETs will turn off. When the V<sub>CC</sub> voltage is higher than 4.0 V, the UVLO flag will be cleared and the soft-start function will activate.

#### Thermal Shutdown

The IC will shutdown if the die temperature exceeds 150°C. The IC will restart with soft-start operation only after the junction temperature drops below 125°C.

Figure 26. Typical Application Circuit

Table 1. Typical Design Value

| For Vcc = 12 V Application |             |              |            |            |            |            |            |           |            |                                               |         |

|----------------------------|-------------|--------------|------------|------------|------------|------------|------------|-----------|------------|-----------------------------------------------|---------|

| Vin<br>(V)                 | Vout<br>(V) | Fsw<br>(kHz) | C1<br>(pF) | C2<br>(nF) | R1<br>(kΩ) | R2<br>(kΩ) | R3<br>(kΩ) | R4<br>(Ω) | C3<br>(pF) | C4 (μF)                                       | L1 (μH) |

| 12                         | 5           | Any          | 10         | 2.0        | 23         | 10         | 1.4        | 200       | 800        | Ceramic 22 μF x 2                             | 5.0     |

| 12                         | 3.3         | Any          | 10         | 2.0        | 23         | 10         | 2.2        | 200       | 800        | Ceramic 22 μF x 2                             | 5.0     |

| 12                         | 1.2         | Any          | 10         | 2.0        | 23         | 10         | 10         | 200       | 800        | Ceramic 22 μF x 2                             | 5.0     |

| 12                         | 5           | Any          | 10         | 2.0        | 54         | 10         | 1.4        | 200       | 800        | SP 100 μF / 12 mΩ                             | 5.0     |

| 12                         | 3.3         | Any          | 10         | 2.0        | 54         | 10         | 2.2        | 200       | 800        | SP 100 μF / 12 mΩ                             | 5.0     |

| 12                         | 1.2         | Any          | 10         | 2.0        | 54         | 10         | 10         | 200       | 800        | SP 100 μF / 12 mΩ                             | 5.0     |

| 12                         | 5           | Any          | 10         | 1.0        | 30         | 10         | 1.4        | NC        | NC         | Electrolytic 470 μF/160 mΩ                    | 5.0     |

| 12                         | 3.3         | Any          | 10         | 1.0        | 30         | 10         | 2.2        | NC        | NC         | Electrolytic 470 μF/160 mΩ                    | 5.0     |

| 12                         | 1.2         | Any          | 10         | 1.0        | 30         | 10         | 10         | NC        | NC         | Electrolytic 470 μF/160 mΩ                    | 5.0     |

| For Vc                     | c = 5 V A   | pplicatio    | n          | •          | •          | •          |            |           |            |                                               |         |

| Vin<br>(V)                 | Vout<br>(V) | Fsw<br>(kHz) | C1<br>(pF) | C2<br>(nF) | R1<br>(kΩ) | R2<br>(kΩ) | R3<br>(kΩ) | R4<br>(Ω) | C3<br>(pF) | C4 (μF)                                       | L1 (μH) |

| 5                          | 3.3         | Any          | 10         | 2.0        | 56         | 10         | 2.2        | 200       | 800        | Ceramic 22 $\mu$ F x 2, ESR = 4 m $\Omega$    | 5.0     |

| 5                          | 1.2         | Any          | 10         | 2.0        | 56         | 10         | 10         | 200       | 800        | Ceramic 22 $\mu$ F x 2, ESR = 4 m $\Omega$    | 5.0     |

| 5                          | 3.3         | Any          | 10         | 2.0        | 100        | 10         | 2.2        | 200       | 800        | SP 100 $\mu$ F / ESR = 12 m $\Omega$          | 5.0     |

| 5                          | 1.2         | Any          | 10         | 2.0        | 100        | 10         | 10         | 200       | 800        | SP 100 $\mu$ F / ESR = 12 m $\Omega$          | 5.0     |

| 5                          | 3.3         | Any          | 10         | 1.0        | 60         | 10         | 2.2        | NC        | NC         | Electrolytic 470 $\mu$ F/ESR = 160 m $\Omega$ | 5.0     |

| 5                          | 1.2         | Any          | 10         | 1.0        | 60         | 10         | 10         | NC        | NC         | Electrolytic 470 $\mu$ F/ESR = 160 m $\Omega$ | 5.0     |

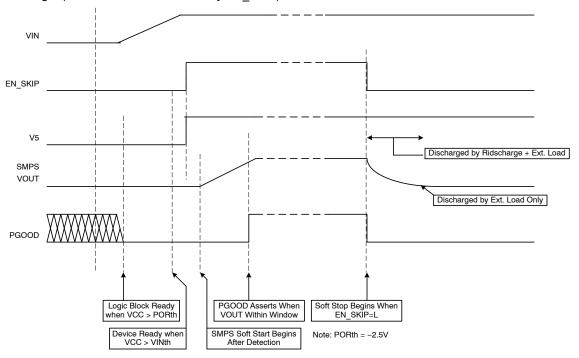

#### **TIMING DIAGRAMS**

Timing 1 (SMPS Enable and Disable by EN\_SKIP)

Figure 27.

Timing 2 (SMPS OVP & UVP Operation)

Figure 28.

回

TOP VIEW

┅┅

SIDE VIEW

DETAIL B

LEA

A1

PIN ONE

LOCATION

2X 0.10 C

2X 0.10 C

// 0.05 C

□ 0.05 C

NOTE 4

Α

В

SEATING PLANE

C

Ē

**DATE 08 OCT 2021**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM THE TERMINAL TIP.

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS.

THE TERMINALS.

DETAIL B

ALTERNATE

CONSTRUCTIONS

DETAIL A

ALTERNATE TERMINAL

CONSTRUCTIONS

|                   | MILLIME  |          |      |  |  |  |

|-------------------|----------|----------|------|--|--|--|

| DIM               | MIN.     | N□M.     | MAX. |  |  |  |

| Α                 | 0.80     | 0.90     | 1.00 |  |  |  |

| A1                | 0.00     | 0.05     |      |  |  |  |

| A3                |          | 0.20 REF |      |  |  |  |

| b                 | 0.18     | 0.30     |      |  |  |  |

| D                 | 3.00 BSC |          |      |  |  |  |

| DS                | 1.65     | 1.85     |      |  |  |  |

| E                 |          | 3.00 BSC | ;    |  |  |  |

| E2                | 1.65     | 1.85     |      |  |  |  |

| е                 | 0.50 BSC |          |      |  |  |  |

| k                 | 0.18 TYP |          |      |  |  |  |

| L                 | 0.30     | 0.50     |      |  |  |  |

| L1                | 0.00     | 0.15     |      |  |  |  |

| E<br>E2<br>e<br>k | 0.30     | 1.85     |      |  |  |  |

#### MOUNTING FOOTPRINT

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

■ = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON04795D     | Electronic versions are uncontrolled except when accessed directly from the Document Rep<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | QFN16 3X3, 0.5P |                                                                                                                                                                             | PAGE 1 OF 1 |  |  |  |

onsemi and ONSemi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMi., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer p

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative