# NCP51190, NCV51190

## 1.5A DDR Memory Termination Regulator

The NCP/NCV51190 is a simple, cost-effective, high-speed linear regulator designed to generate the  $V_{TT}$  termination voltage rail for DDR-I, DDR-II and DDR-III memory. The regulator is capable of actively sourcing or sinking up to  $\pm 1.5$  A for DDR-I, or up to  $\pm 0.5$  A for DDR-II /-III while regulating the output voltage to within  $\pm 30$  mV.

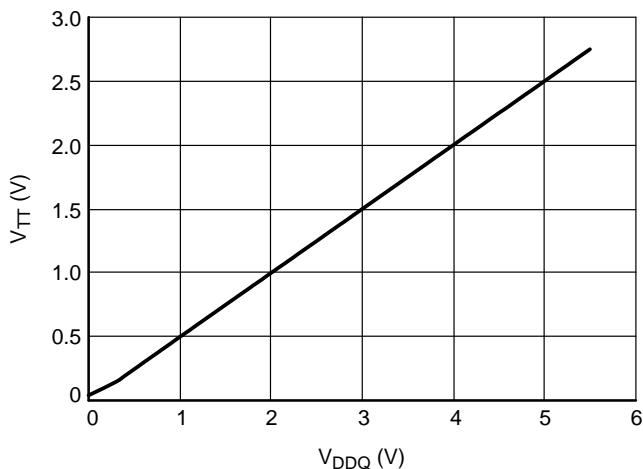

The output termination voltage is tightly regulated to track  $V_{TT} = (V_{DDQ}/2)$  over the entire current range.

The NCP/NCV51190 incorporates a high-speed differential amplifier to provide ultra-fast response to line and load transients. Other features include extremely low initial offset voltage, excellent load regulation, source/sink soft-start and on-chip thermal shut-down protection.

The NCP/NCV51190 features the power-saving Suspend To Ram (STR) function which will tri-state the regulator output and lower the quiescent current drawn when the /SS pin is pulled low.

The NCP/NCV51190 is available in a DFN8 package.

### Features

- Generate DDR Memory Termination Voltage ( $V_{TT}$ )

- For DDR-I, DDR-II, DDR-III Source / Sink Currents

- Supports DDR-I to  $\pm 1.5$  A, DDR-II, DDR-III to  $\pm 0.5$  A (peak)

- Integrated Power MOSFETs with Thermal Protection

- Stable with 10  $\mu$ F Ceramic  $V_{TT}$  Capacitor

- High Accuracy Output Voltage at Full-Load

- Minimal External Component Count

- Shutdown for Standby or Suspend to RAM (STR) mode

- Built-in Soft Start

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These are Pb-Free Devices

### Applications

- Desktop PC's, Notebooks, and Workstations

- Graphics Card DDR Memory Termination

- Set Top Boxes, Digital TV's, Printers

- Embedded Systems

- Active Bus Termination

**ON Semiconductor®**

[www.onsemi.com](http://www.onsemi.com)

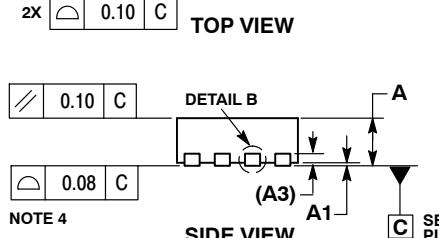

### MARKING DIAGRAM

DFN8

MN SUFFIX

CASE 506AA

XX = Specific Device Code

M = Date Code

■ = Pb-Free Device

(Note: Microdot may be in either location)

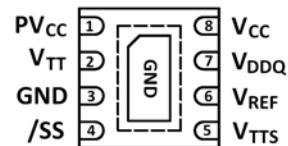

### PIN CONNECTION

### ORDERING INFORMATION

See detailed ordering, marking and shipping information in the package dimensions section on page 8 of this data sheet.

# NCP51190, NCV51190

## 1.5 A, DDR-I /-II /-III TERMINATION REGULATOR

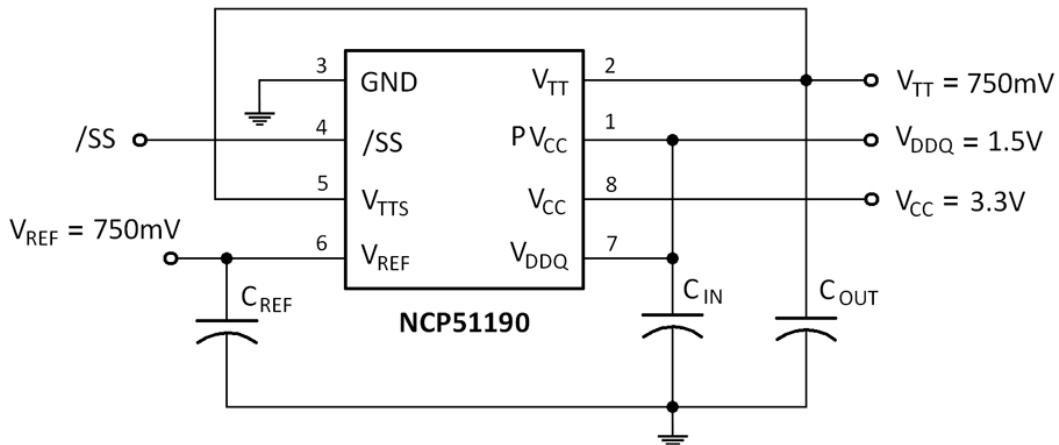

Figure 1. Typical Application Schematic

### PIN FUNCTION DESCRIPTION – NCP51190

| Pin Number | Pin Name    | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | $PV_{CC}$   | The $PV_{CC}$ pin provides the rail voltage from where the $V_{TT}$ pin draws load current. There is a limitation between $V_{CC}$ and $PV_{CC}$ . The $PV_{CC}$ voltage must be less or equal to the $V_{CC}$ voltage to ensure the correct output voltage regulation. The $V_{TT}$ source current capability is dependent on $PV_{CC}$ voltage. The higher the voltage on $PV_{CC}$ , the higher the source current. |

| 2          | $V_{TT}$    | Regulator output voltage capable of sinking and sourcing current while regulating the output rail.                                                                                                                                                                                                                                                                                                                     |

| 3          | GND         | Common Ground.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4          | /SS         | Suspend Shutdown supports Suspend To RAM function. CMOS compatible input sets $V_{TT}$ output to high impedance state. Logic HI = Enable, Logic LO = Shutdown.                                                                                                                                                                                                                                                         |

| 5          | $V_{TTS}$   | $V_{TTS}$ is the $V_{TT}$ sense input.                                                                                                                                                                                                                                                                                                                                                                                 |

| 6          | $V_{REF}$   | $V_{REF}$ is an output pin that provides the buffered output of the internal reference voltage equal to half of $V_{DDQ}$ . Two resistors dividing down the $V_{DDQ}$ voltage on the pin to create the regulated output voltage.                                                                                                                                                                                       |

| 7          | $V_{DDQ}$   | The $V_{DDQ}$ pin is an input pin for creating the internal reference voltage to regulate $V_{TT}$ . The $V_{DDQ}$ voltage is connected to an internal resistor divider. The central tap of resistor divider ( $V_{DDQ}/2$ ) is connected to the internal voltage buffer, which output is connected to $V_{REF}$ pin and the non-inverting input of the error amplifier as the reference voltage.                      |

| 8          | $V_{CC}$    | Power for the analog control circuitry.                                                                                                                                                                                                                                                                                                                                                                                |

|            | THERMAL PAD | Pad for thermal connection. The exposed pad must be connected to the ground plane using multiple vias for maximum power dissipation performance.                                                                                                                                                                                                                                                                       |

# NCP51190, NCV51190

## ABSOLUTE MAXIMUM RATINGS

| Rating                                                                                           | Symbol          | Value       | Unit |

|--------------------------------------------------------------------------------------------------|-----------------|-------------|------|

| $V_{CC}$ , $PV_{CC}$ , $V_{DDQ}$ , /SS to GND (Note 1)                                           |                 | -0.3 to +6  | V    |

| Storage Temperature                                                                              | $T_{stg}$       | -65 to +150 | °C   |

| Operating Junction Temperature Range                                                             | $T_J$           | -40 to +125 | °C   |

| Thermal Characteristics, SO8-EP Thermal Resistance, Junction-to-Air Power Rating at 25°C ambient | $R_{\theta JA}$ | TBD         | °C/W |

| ESD Capability, Human Body Model (Note 2)                                                        | $ESD_{HBM}$     | 2000        | V    |

| ESD Capability, Machine Model (Note 2)                                                           | $ESD_{MM}$      | 150         | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. No pin to exceed  $V_{CC}$ . Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

2. This device series incorporates ESD protection and is tested by the following method:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

Latchup Current Maximum Rating tested per JEDEC standard: JESD78.

## RECOMMENDED OPERATING CONDITIONS

| Rating                  | Symbol    | Value       | Unit |

|-------------------------|-----------|-------------|------|

| Bias Supply Voltage     | $V_{CC}$  | 2.2 to 5.5  | V    |

| Input Voltage           | $PV_{CC}$ | 1.35 to 2.5 | V    |

| Reference Input Voltage | $V_{DDQ}$ | 1.35 to 2.7 | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

## ELECTRICAL CHARACTERISTICS

$-40^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ ;  $V_{CC} = PV_{CC} = V_{DDQ} = 2.5$  V; unless otherwise noted. Typical values are at  $T_J = +25^{\circ}\text{C}$

| Parameter                                                  | Condition                                                                                                       | Symbol                 | Min                          | Typ                          | Max                          | Unit      |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------|------------------------------|------------------------------|------------------------------|-----------|

| Reference Voltage (DDR I)<br>$I_{REF} = 0$ mA (unloaded)   | $PV_{CC} = V_{DDQ} = 2.3$ V<br>$= 2.5$ V<br>$= 2.7$ V                                                           | $V_{REF}$<br>(DDR-I)   | 1.125<br>1.225<br>1.325      | 1.151<br>1.251<br>1.351      | 1.175<br>1.275<br>1.375      | V         |

| Reference Voltage (DDR II)<br>$I_{REF} = 0$ mA (unloaded)  | $PV_{CC} = V_{DDQ} = 1.7$ V<br>$= 1.8$ V<br>$= 1.9$ V                                                           | $V_{REF}$<br>(DDR-II)  | 0.830<br>0.880<br>0.925      | 0.851<br>0.901<br>0.951      | 0.880<br>0.930<br>0.975      | V         |

| Reference Voltage (DDR III)<br>$I_{REF} = 0$ mA (unloaded) | $PV_{CC} = V_{DDQ} = 1.35$ V<br>$= 1.5$ V<br>$= 1.6$ V                                                          | $V_{REF}$<br>(DDR-III) | 0.660<br>0.735<br>0.785      | 0.676<br>0.751<br>0.801      | 0.695<br>0.770<br>0.820      | V         |

| $V_{REF}$ – Output Impedance                               | $I_{REF} = -30$ $\mu$ A to $+30$ $\mu$ A                                                                        | $Z_{REF}$              |                              | 2.5                          |                              | $k\Omega$ |

| $V_{TT}$ Output Voltage<br>(DDR-I)                         | $I_{OUT} = 0$ A<br>$PV_{CC} = V_{DDQ} = 2.3$ V<br>$PV_{CC} = V_{DDQ} = 2.5$ V<br>$PV_{CC} = V_{DDQ} = 2.7$ V    | $V_{TT}$<br>(DDR-I)    | –<br>1.112<br>1.202<br>1.312 | –<br>1.150<br>1.250<br>1.350 | –<br>1.182<br>1.282<br>1.382 | V         |

|                                                            | $I_{OUT} = +1.5$ A<br>$PV_{CC} = V_{DDQ} = 2.3$ V<br>$PV_{CC} = V_{DDQ} = 2.5$ V<br>$PV_{CC} = V_{DDQ} = 2.7$ V | $V_{TT}$<br>(DDR-I)    | –<br>1.115<br>1.215<br>1.315 | –<br>1.150<br>1.250<br>1.350 | –<br>1.185<br>1.285<br>1.385 |           |

|                                                            | $I_{OUT} = -1.5$ A<br>$PV_{CC} = V_{DDQ} = 2.3$ V<br>$PV_{CC} = V_{DDQ} = 2.5$ V<br>$PV_{CC} = V_{DDQ} = 2.7$ V | $V_{TT}$<br>(DDR-I)    | –<br>1.117<br>1.217<br>1.317 | –<br>1.150<br>1.250<br>1.350 | –<br>1.182<br>1.282<br>1.382 |           |

# NCP51190, NCV51190

## ELECTRICAL CHARACTERISTICS

$-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ ;  $V_{\text{CC}} = PV_{\text{CC}} = V_{\text{DDQ}} = 2.5 \text{ V}$ ; unless otherwise noted. Typical values are at  $T_J = +25^\circ\text{C}$

| Parameter                                           | Condition                                                                                                                                                                                        | Symbol                       | Min                          | Typ                          | Max                          | Unit             |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|------------------|

| $V_{\text{TT}}$ Output Voltage (DDR-II)             | $I_{\text{OUT}} = 0 \text{ A}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.7 \text{ V}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.8 \text{ V}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.9 \text{ V}$    | $V_{\text{TT}}$<br>(DDR-II)  | —<br>0.816<br>0.866<br>0.916 | —<br>0.850<br>0.900<br>0.950 | —<br>0.881<br>0.931<br>0.981 | V                |

|                                                     | $I_{\text{OUT}} = +0.5 \text{ A}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.7 \text{ V}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.8 \text{ V}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.9 \text{ V}$ | $V_{\text{TT}}$<br>(DDR-II)  | —<br>0.815<br>0.863<br>0.914 | —<br>0.851<br>0.900<br>0.950 | —<br>0.885<br>0.933<br>0.984 |                  |

|                                                     | $I_{\text{OUT}} = -0.5 \text{ A}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.7 \text{ V}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.8 \text{ V}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.9 \text{ V}$ | $V_{\text{TT}}$<br>(DDR-II)  | —<br>0.814<br>0.862<br>0.913 | —<br>0.850<br>0.900<br>0.950 | —<br>0.884<br>0.932<br>0.983 |                  |

|                                                     | $I_{\text{OUT}} = 0 \text{ A}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.35 \text{ V}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.5 \text{ V}$<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.6 \text{ V}$   | $V_{\text{TT}}$<br>(DDR-III) | —<br>0.650<br>0.725<br>0.775 | —<br>0.675<br>0.750<br>0.800 | —<br>0.700<br>0.775<br>0.825 |                  |

|                                                     | $I_{\text{OUT}} = +0.2 \text{ A}$ ,<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.35 \text{ V}$<br>$I_{\text{OUT}} = -0.2 \text{ A}$ ,<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.35 \text{ V}$           | $V_{\text{TT}}$<br>(DDR-III) | —<br>0.649<br>—<br>0.640     | —<br>0.675<br>—<br>0.675     | —<br>0.700<br>—<br>0.700     |                  |

|                                                     | $I_{\text{OUT}} = +0.4 \text{ A}$ ,<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.5 \text{ V}$<br>$I_{\text{OUT}} = -0.4 \text{ A}$ ,<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.5 \text{ V}$             | $V_{\text{TT}}$<br>(DDR-III) | —<br>0.722<br>—<br>0.725     | —<br>0.751<br>—<br>0.750     | —<br>0.776<br>—<br>0.774     |                  |

|                                                     | $I_{\text{OUT}} = +0.5 \text{ A}$ ,<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.6 \text{ V}$<br>$I_{\text{OUT}} = -0.5 \text{ A}$ ,<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.6 \text{ V}$             | $V_{\text{TT}}$<br>(DDR-III) | —<br>0.773<br>—<br>0.775     | —<br>0.801<br>—<br>0.800     | —<br>0.827<br>—<br>0.824     |                  |

|                                                     | $I_{\text{OUT}} = \pm 1.5 \text{ A}$ ,<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 2.5 \text{ V}$                                                                                                      | $V_{\text{OS}}$<br>(DDR-I)   | -30                          | 0                            | +30                          | mV               |

|                                                     | $I_{\text{OUT}} = \pm 0.5 \text{ A}$ ,<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.8 \text{ V}$                                                                                                      | $V_{\text{OS}}$<br>(DDR-II)  | -30                          | 0                            | +30                          |                  |

|                                                     | $I_{\text{OUT}} = \pm 0.5 \text{ A}$ ,<br>$PV_{\text{CC}} = V_{\text{DDQ}} = 1.5 \text{ V}$                                                                                                      | $V_{\text{OS}}$<br>(DDR-III) | -30                          | 0                            | +30                          |                  |

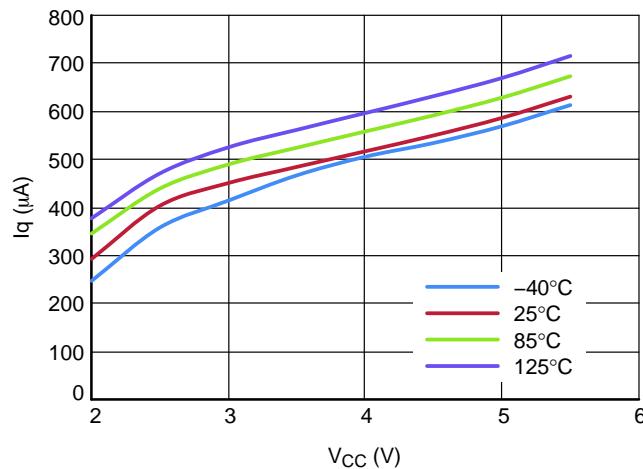

| Quiescent Current                                   | $I_{\text{OUT}} = 0 \text{ A}$                                                                                                                                                                   | $I_Q$                        |                              | 380                          | 500                          | $\mu\text{A}$    |

| $V_{\text{DDQ}}$ Input Impedance                    |                                                                                                                                                                                                  | $Z_{\text{VDDQ}}$            |                              | 100                          |                              | $\text{k}\Omega$ |

| /SS Leakage Current                                 | $/\text{SS} = 0 \text{ V}$                                                                                                                                                                       | $I_{\text{L_SS}}$            |                              | 2                            | 5                            | $\mu\text{A}$    |

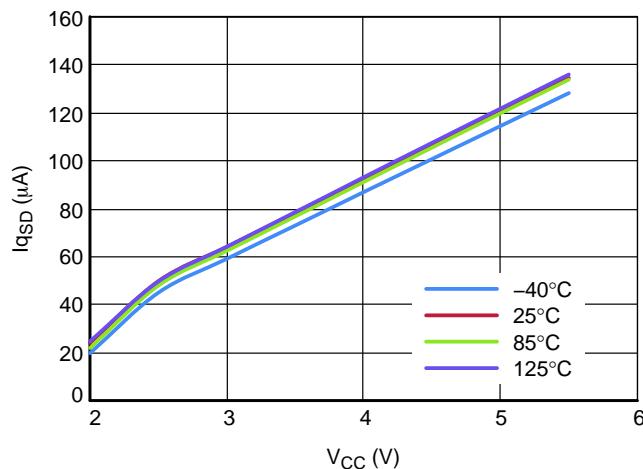

| Quiescent Current in Suspend Shutdown               | $/\text{SS} = 0 \text{ V}$                                                                                                                                                                       | $I_{\text{Q_SS}}$            |                              | 115                          | 150                          | $\mu\text{A}$    |

| Suspend Shutdown Threshold                          |                                                                                                                                                                                                  | $V_{\text{IH}}$              | 1.9                          |                              |                              | V                |

|                                                     |                                                                                                                                                                                                  | $V_{\text{IL}}$              |                              |                              | 0.8                          |                  |

| $V_{\text{TT}}$ leakage Current in Suspend Shutdown | $/\text{SS} = 0 \text{ V}$ , $V_{\text{TT}} = 1.25 \text{ V}$                                                                                                                                    | $I_{\text{L_VTT}}$           |                              | 1                            | 10                           | $\mu\text{A}$    |

| $V_{\text{TTS}}$ Current                            |                                                                                                                                                                                                  | $I_{\text{TTS}}$             |                              | 13                           |                              | nA               |

| Thermal Shutdown Temperature                        |                                                                                                                                                                                                  | $T_{\text{SD}}$              |                              | 165                          |                              | $^\circ\text{C}$ |

| Thermal Shutdown Hysteresis                         |                                                                                                                                                                                                  | $T_{\text{SH}}$              |                              | 10                           |                              | $^\circ\text{C}$ |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

# NCP51190, NCV51190

## TYPICAL PERFORMANCE CHARACTERISTICS

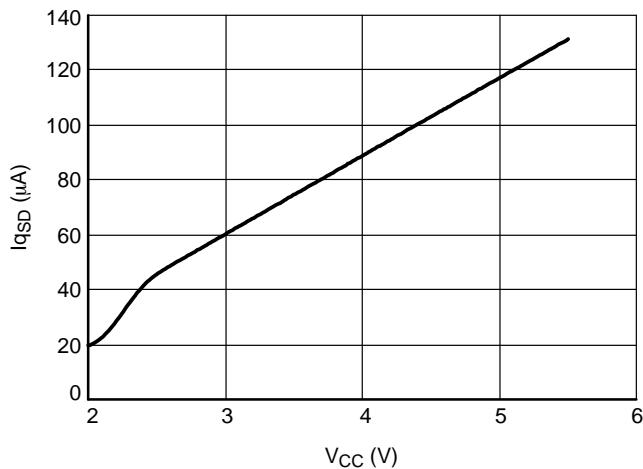

Figure 2.  $I_{qSD}$  vs.  $V_{CC}$

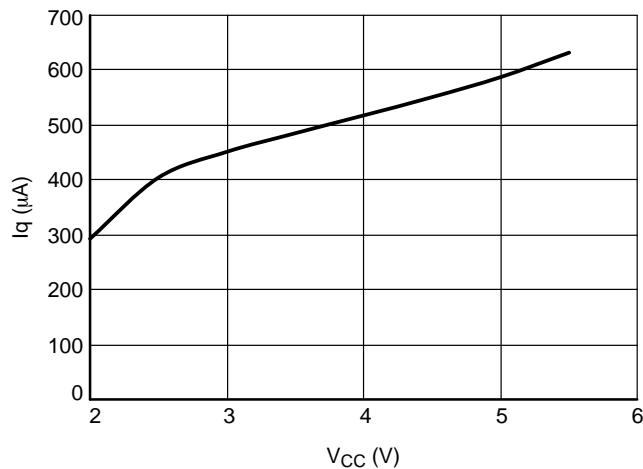

Figure 3.  $I_q$  vs.  $V_{CC}$

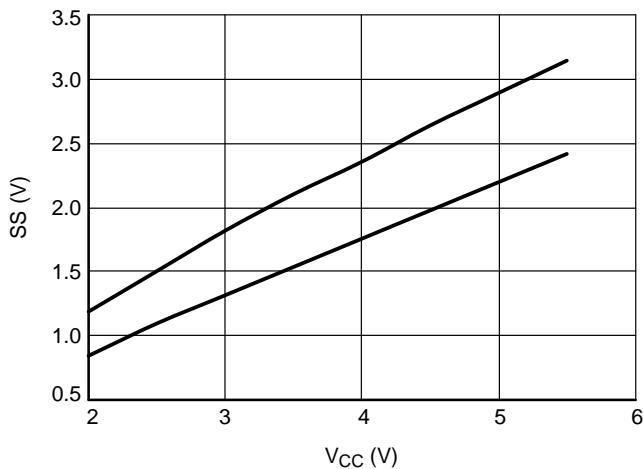

Figure 4.  $V_{IH}$  and  $V_{IL}$

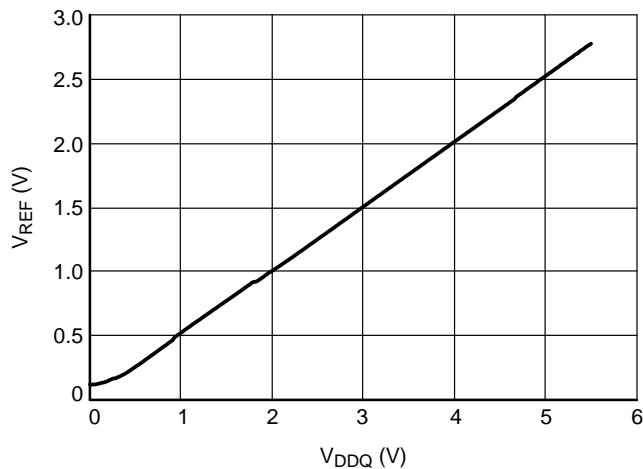

Figure 5.  $V_{REF}$  vs.  $V_{DDQ}$

Figure 6.  $V_{TT}$  vs.  $V_{DDQ}$

Figure 7.  $I_{qSD}$  vs.  $V_{CC}$  over Temperature

# NCP51190, NCV51190

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 8.  $I_q$  vs.  $V_{CC}$  over Temperature

## General

The NCP/NCV51190 is a bus termination, linear regulator designed to meet the JEDEC requirements for DDR-I, DDR-II and DDR-III memory termination. The NCP/NCV51190 is capable of sourcing and sinking current while accurately tracking and regulating the  $V_{TT}$  output voltage equal to  $(V_{DDQ} / 2)$ . The output stage has been designed to maintain excellent load regulation and preventing shoot-through. The NCP/NCV51190 uses two distinct power rails to separate the analog circuitry from the power output stage and decrease internal power dissipation.

## Supply Voltage Inputs

For added flexibility, separate input pins ( $V_{CC}$  and  $PV_{CC}$ ) are provided for each required supply input.  $V_{CC}$  is used to supply all the internal control circuitry and  $PV_{CC}$  is used exclusively to provide the rail voltage for the output stage used to create  $V_{TT}$ . These pins have the capability to work off separate supplies with the condition that  $V_{CC}$  is always greater than or equal to  $PV_{CC}$ , and should always be used with either a 1.8 V or 2.5 V rail. If the junction temperature exceeds the thermal shutdown threshold, the part will enter a shutdown state identical to the manual shutdown where  $V_{TT}$  is tri-stated and  $V_{REF}$  remains active. Lower voltage rails, such as 1.5 V can be used but will reduce the maximum available output current.

## Generation of Internal Voltage Reference

$V_{DDQ}$  is the input used to create the internal reference voltage for regulating  $V_{TT}$ . The reference voltage is generated from a resistor divider of two internal 50 k $\Omega$  resistors. This guarantees that  $V_{TT}$  will precisely track  $(V_{DDQ} / 2)$ . The optimal implementation of the  $V_{DDQ}$  input pin is as a remote sense. This can be achieved by connecting  $V_{DDQ}$  directly to the 1.8 V rail at the DIMM memory module instead of connecting it to  $PV_{CC}$ . This ensures that the reference voltage precisely tracks the DDR memory power rail without introducing a large voltage drop due to power traces. For DDR-II applications the  $V_{DDQ}$  input will be 1.8 V, which will create a  $(V_{DDQ} / 2) = 0.9$  V termination voltage at the  $V_{TT}$  output.

$V_{REF}$  provides a buffered output of the internal reference voltage  $(V_{DDQ} / 2)$ . For improved performance, an output bypass capacitor can be placed, close to the pin, to help reduce any potential stray noise. A ceramic capacitor in the range of 0.01  $\mu$ F to 0.1  $\mu$ F is recommended. The  $V_{REF}$  output remains active during the shutdown state and thermal shutdown events for the suspend to RAM functionality.

## Remote Voltage Feedback Sensing

The purpose of the  $V_{TTS}$  sense pin is to provide improved remote load regulation. In most motherboard applications, the termination resistors will connect to  $V_{TT}$  in a long plane. If the output voltage was regulated only at the output of the NCP/NCV51190, then any long traces will generate a

significant IR drop resulting in a sagging termination voltage at one end of the bus than the other. The  $V_{TTS}$  pin can be used to improve performance by connecting it to the middle of the bus. This will provide better power distribution across the entire termination bus. If remote load regulation is not used, then the  $V_{TTS}$  pin must still be connected to  $V_{TT}$ . Care should be taken when a long  $V_{TTS}$  trace is implemented in close proximity to the memory. Noise pickup in the  $V_{TTS}$  trace can cause problems with precise regulation of  $V_{TT}$ . A small 0.1  $\mu$ F ceramic capacitor placed next to the  $V_{TTS}$  pin can help filter out any high frequency noise and thereby keeping the  $V_{TT}$  power rail in spec.

## Regulator Shutdown Function

The NCP/NCV51190 contains an active low enable pin (/SS) that can be used for suspend to RAM functionality. In this condition the  $V_{TT}$  output will tri-state, with the  $V_{REF}$  output remaining active in order to provide a constant reference signal for the memory and chipset. During shutdown,  $V_{TT}$  should not be exposed to voltages that exceed  $PV_{CC}$ .

With the enable pin asserted low the quiescent current of the NCP/NCV51190 will drop, however the  $V_{DDQ}$  input pin will always draw a constant current due to the integrated 100 k $\Omega$  impedance used for generating the internal reference. Therefore, to calculate the total power loss in shutdown, both currents need to be considered. The enable pin also has an internal pull-up current. Therefore, to turn the part on, the enable pin can either be connected to  $V_{CC}$  or left open.

## Termination Voltage Output Regulation

$V_{TT}$  is the regulated output that is used to terminate the bus resistors. It is capable of sourcing and sinking current while regulating the output precisely to  $V_{DDQ} / 2$ . The NCP/NCV51190 is designed to handle continuous currents of up to  $\pm 1.5$  A with excellent load regulation. If a transient is expected to last above the maximum continuous current rating for a significant amount of time, then the bulk output capacitor should be sized large enough to prevent an excessive voltage drop.

## Thermal Shutdown with Hysteresis

If the NCP/NCV51190 is to operate in elevated temperatures for long durations, care should be taken to ensure that the maximum operating junction temperature is not exceeded. To guarantee safe operation, the NCP/NCV51190 provides on-chip thermal shutdown protection. When the chip junction temperature exceeds 165°C (typical) the part will shutdown. When the junction temperature falls back to 155°C (typical) the device resumes normal operation. If the junction temperature exceeds the thermal shutdown threshold,  $V_{TT}$  will tri-state until the part returns below the temperature hysteresis trip-point.

## NCP51190, NCV51190

**Table 1. ORDERING INFORMATION**

| Device         | Marking | Package           | Shipping †         |

|----------------|---------|-------------------|--------------------|

| NCP51190MNTAG  | A5      | DFN8<br>(Pb-Free) | 3000 / Tape & Reel |

| NCV51190MNTAG* | CC      |                   |                    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

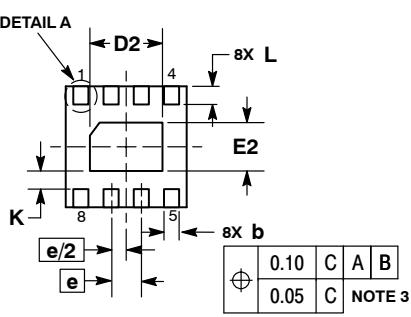

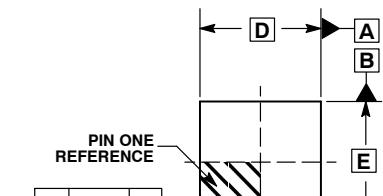

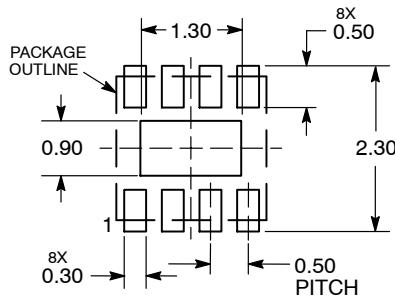

# MECHANICAL CASE OUTLINE

## PACKAGE DIMENSIONS

ON Semiconductor®

SCALE 4:1

DFN8 2x2, 0.5P

CASE 506AA-01

ISSUE E

DATE 22 JAN 2010

NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.20 MM FROM TERMINAL TIP.

4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

| DIM | MILLIMETERS |      |

|-----|-------------|------|

|     | MIN         | MAX  |

| A   | 0.80        | 1.00 |

| A1  | 0.00        | 0.05 |

| A3  | 0.20 REF    |      |

| b   | 0.20        | 0.30 |

| D   | 2.00 BSC    |      |

| D2  | 1.10        | 1.30 |

| E   | 2.00 BSC    |      |

| E2  | 0.70        | 0.90 |

| e   | 0.50 BSC    |      |

| K   | 0.30 REF    |      |

| L   | 0.25        | 0.35 |

| L1  | ---         | 0.10 |

DETAIL A

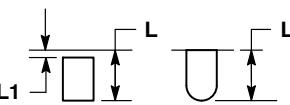

OPTIONAL CONSTRUCTIONS

DETAIL B

OPTIONAL CONSTRUCTION

GENERIC

MARKING DIAGRAM\*

XX = Specific Device Code

M = Date Code

▪ = Pb-Free Device

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "▪", may or may not be present.

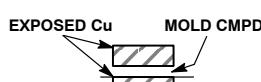

RECOMMENDED

SOLDERING FOOTPRINT\*

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

|                  |                            |                                                                                                                                                                                     |

|------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOCUMENT NUMBER: | 98AON18658D                | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |

| DESCRIPTION:     | DFN8, 2.0X2.0, 0.5MM PITCH | PAGE 1 OF 1                                                                                                                                                                         |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

**onsemi, ONSEMI, and other names, marks, and brands** are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "**onsemi**" or its affiliates and/or subsidiaries in the United States and/or other countries. **onsemi** owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of **onsemi**'s product/patent coverage may be accessed at [www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf). **onsemi** reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and **onsemi** makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Email Requests to: [orderlit@onsemi.com](mailto:orderlit@onsemi.com)

**onsemi** Website: [www.onsemi.com](http://www.onsemi.com)

### TECHNICAL SUPPORT

#### North American Technical Support:

Voice Mail: 1 800-282-9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

#### Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative