## Octal, RS-232/RS-423 Line Driver

### ADM5170

#### **FEATURES**

Eight Single Ended Line Drivers in One Package Meets EIA Standard RS-232E, RS-423A and CCITT V.10/X.26 Resistor Programmable Slew Rate Wide Supply Voltage Range Low Power CMOS 3-State Outputs TTL/CMOS Compatible Inputs Output Short Circuit Protection Available in 28-Lead PLCC Low Power Replacement for UC5170C

APPLICATIONS High Speed Communication Computer I-O Ports Peripherals High Speed Modems Printers Logic Level Translation

#### **GENERAL DESCRIPTION**

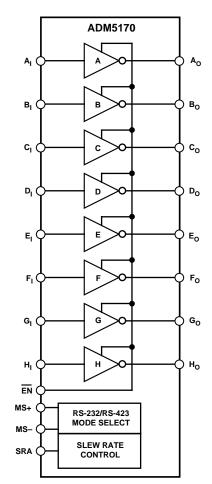

The ADM5170 is an octal line driver suitable for digital communication systems with data rates up to 116 kB/s. Input TTL or CMOS signal levels are inverted and translated into either EIA RS-232E or RS-423A signal levels depending on the status of the Mode Select inputs MS+ and MS-. With both Mode Select inputs at GND, RS-423 operation is selected while with MS+ connected to  $V_{DD}$  and MS- connected to  $V_{SS}$ , RS-232 operation is selected.

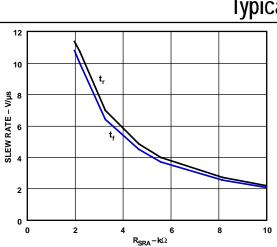

The output slew rates may be controlled using an external resistor connected between the SRA (Slew Rate Adjust) pin and GND. Resistor values between 2 k $\Omega$  and 10 k $\Omega$  may be selected giving a slew rate which can be adjusted from 10 V/µs to 2.2 V/µs. This adjustment of the slew rate allows tailoring of the output characteristics to suit the interface cable being used.

The outputs may be disabled using the  $\overline{EN}$  (Enable Input). This feature permits sharing of a common output line.

The ADM5170 is fabricated on an advanced CMOS process featuring low power consumption. In the disabled state the power consumption reduces from 500 mW to 40 mW. The ADM5170 is available in a 28-lead PLCC package.

#### FUNCTIONAL BLOCK DIAGRAM

**Truth Table**

| Inputs<br>EN | Data | Outputs<br>EIA RS-232E <sup>1</sup> | RS-423A      |

|--------------|------|-------------------------------------|--------------|

| 0            | 0    | (V <sub>DD</sub> - 3 V)             | 5 V to 6 V   |

| 0            | 1    | (V <sub>ss</sub> - 3 V)             | -5 V to -6 V |

| 1            | X    | High Z                              | High Z       |

<sup>1</sup>Minimum Output Level

#### REV.A

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood. MA 02062-9106, U.S.A Tel: 781.329.4700 ©1993–2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# $\label{eq:stable} ADM5170-SPECIFICATIONS ~ (V_{DD} = +10 \ V \pm 10\%, \ V_{SS} = -10 \ V \pm 10\% \ V, \ MS + = MS - = 0 \ V, \ R_{SRA} = 10 \ k\Omega. \ All \ Specifications \ T_{MIN} \ to \ T_{MAX} \ unless \ otherwise \ noted.)$

| Parameter                                   | Min  | Тур  | Max             | Units | <b>Test Conditions/Comments</b>                                                                                                 |

|---------------------------------------------|------|------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------|

| POWER REQUIREMENTS                          |      |      |                 |       |                                                                                                                                 |

| V <sub>DD</sub> Range                       | 9    |      | 15              | V     |                                                                                                                                 |

| V <sub>ss</sub> Range                       | -9   |      | -15             | V     |                                                                                                                                 |

| $I_{DD}$ (Disabled)                         |      | 2    | 4               | mA    | $\overline{\mathrm{EN}} = \mathrm{High},$                                                                                       |

| $I_{\rm DD}$ (Enabled)                      |      | 25   | 36              | mA    | $R_{\rm L} = \infty,  \overline{\rm EN} = 0  {\rm V}$                                                                           |

| I <sub>ss</sub> (Disabled)                  |      | -2   | -4              | mA    | $\frac{H_L}{EN} = High$                                                                                                         |

| I <sub>ss</sub> (Enabled)                   |      | -23  | -36             | mA    | $R_{\rm L} = \infty, \ \overline{\rm EN} = 0 \ {\rm V}$                                                                         |

| DIGITAL INPUTS                              |      |      |                 |       |                                                                                                                                 |

| Input Logic Threshold High, $V_{INH}$       | 2.0  |      |                 | V     |                                                                                                                                 |

| Input Logic Threshold Low, V <sub>INI</sub> |      |      | 0.8             | V     |                                                                                                                                 |

| Input Clamp Voltage, V <sub>INK</sub>       |      | -1.1 | -1.8            | V     | $I_{IN} = -15 \text{ mA}$                                                                                                       |

| Input High Level Current, I <sub>INH</sub>  |      |      | 1               | μA    | $V_{\rm INH} = 2.4  \rm V$                                                                                                      |

| Input Low Level Current, I <sub>INL</sub>   | -1   |      |                 | μA    | $V_{\rm INL} = 0.4  \rm V$                                                                                                      |

| OUTPUTS                                     |      |      |                 |       |                                                                                                                                 |

| RS-423A Outputs                             |      |      |                 |       | $\overline{\text{EN}} = 0.8 \text{ V}, \text{ MS+} = \text{MS-} = 0 \text{ V}$                                                  |

| High Level Output Voltage                   | 5.0  | 5.3  | 6.0             | V     | $R_{L} = \infty, V_{IN} = 0.8 V$                                                                                                |

| 0 1 0                                       | 5.0  | 5.3  | 6.0             | V     | $R_{\rm L} = 3 \ \mathrm{k}\Omega, \ V_{\rm IN} = 0.8 \ \mathrm{V}$                                                             |

|                                             | 4.5  | 5.2  | 6.0             | V     | $R_{\rm L} = 450 \ \Omega, \ V_{\rm IN} = 0.8 \ V$                                                                              |

| Low Level Output Voltage                    | -5.0 | -5.3 | -6.0            | V     | $R_{\rm L} = \infty, V_{\rm IN} = 2.0 \text{ V}$                                                                                |

| r o                                         | -5.0 | -5.6 | -6.0            | V     | $R_{\rm L} = 3 \ {\rm k}\Omega, \ V_{\rm IN} = 2.0 \ {\rm V}$                                                                   |

|                                             | -4.5 | -5.4 | -6.0            | V     | $R_{\rm L} = 450 \ \Omega, \ V_{\rm IN} = 2.0 \ V$                                                                              |

| Output Balance, V <sub>BAL</sub>            |      | 0.05 | 0.4             | V     | $R_L = 450 \Omega$ , $V_{BAL} = V_{OH} - V_{OL}$                                                                                |

| RS-232 Outputs                              |      |      |                 |       | $\overline{\text{EN}} = 0.8 \text{ V}, \text{ MS} + = \text{V}_{\text{DD}}, \text{ MS} - = \text{V}_{\text{SS}}$                |

| High Level Output Voltage                   | 7.0  | 7.6  | $V_{DD}$        | V     | $R_{\rm L} = \infty, V_{\rm IN} = 0.8 \text{ V}$                                                                                |

|                                             | 7.0  | 7.6  | V <sub>DD</sub> | V     | $R_{\rm L} = 3 \ k\Omega, \ V_{\rm IN} = 0.8 \ V$                                                                               |

| Low Level Output Voltage                    | -7.0 | -7.7 | V <sub>ss</sub> | V     | $R_{\rm L} = \infty, V_{\rm IN} = 2.0 \text{ V}$                                                                                |

|                                             | -7.0 | -7.7 | Vss             | V     | $R_{\rm L} = 3 \text{ k}\Omega, V_{\rm IN} = 2.0 \text{ V}$                                                                     |

| Off-State Output Current, I <sub>oz</sub>   | -100 |      | 100             | μA    | $\overline{EN} = 2.0 \text{ V}, \text{ V}_{O} = \pm 6 \text{ V}, \text{ V}_{DD} = 15 \text{ V}, \text{ V}_{SS} = -15 \text{ V}$ |

| Short Circuit Current, I <sub>os</sub>      | 15   | 50   | 100             | mA    | $V_{IN} = 0 V, \overline{EN} = 0 V$                                                                                             |

|                                             | 15   | 40   | 100             | mA    | $V_{\rm IN} = 5 \text{ V}, \ \overline{\rm EN} = 0 \text{ V}$                                                                   |

Specifications subject to change without notice.

# TIMING CHARACTERISTICS ( $V_{DD} = +10 V \pm 10\%$ , $V_{SS} = -10 V \pm 10\%$ , MS+ = MS- = 0 V. All Specifications T<sub>MIN</sub> to T<sub>MAX</sub> unless otherwise noted.)

| Parameter                                   | Min  | Тур | Max | Units | Test Conditions/Comments                                                                  |

|---------------------------------------------|------|-----|-----|-------|-------------------------------------------------------------------------------------------|

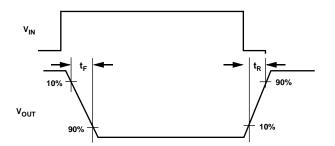

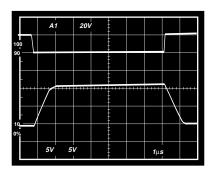

| Output Slew Rate                            |      |     |     |       | Fig 1, Fig 2. $R_{SRA} = 2 k\Omega$ , $R_L = 450 \Omega$ , $C_L = 50 pF$                  |

|                                             | 6.65 | 10  | 14  | V/µs  | Rising/Falling Edge, $t_R$ , $t_F$                                                        |

| Output Slew Rate                            |      |     |     |       | Fig 1, Fig 2. $R_{SRA} = 10 \text{ k}\Omega$ , $R_L = 450 \Omega$ , $C_L = 50 \text{ pF}$ |

| -                                           | 1.33 | 2.0 | 3   | V/µs  | Rising/Falling Edge, $t_R$ , $t_F$                                                        |

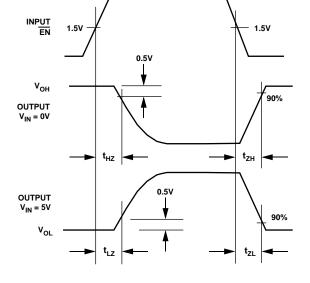

| Output to Hi-Z Propagation Delay (Disable)  |      |     |     | •     | Fig 1, Fig 3. $R_{SRA} = 10 \text{ k}\Omega$ , $R_L = 450 \Omega$ , $C_L = 50 \text{ pF}$ |

|                                             |      | 0.3 | 1.0 | μs    | t <sub>HZ</sub>                                                                           |

|                                             |      | 0.5 | 1.0 | μs    | t <sub>LZ</sub>                                                                           |

| Hi-Z to Valid Output Propagation Delay (Ena | ble) |     |     |       | Fig 1, Fig 3. $R_{SRA} = 10 \text{ k}\Omega$ , $R_L = 450\Omega$ , $C_L = 50 \text{ pF}$  |

|                                             |      | 6.0 | 15  | μs    | t <sub>zH</sub>                                                                           |

|                                             |      | 7.0 | 15  | μs    | t <sub>ZL</sub>                                                                           |

Specifications subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS\***

| $(T_{A} = 25^{\circ}C \text{ unless otherwise noted})$         |

|----------------------------------------------------------------|

| $V_{DD}^{"}$                                                   |

| V <sub>ss</sub> 15 V                                           |

| Input Voltages                                                 |

| $V_{\rm IN}$ 0.3 to $(V_{\rm DD} + 0.3 \text{ V})$             |

| Ouput Voltages                                                 |

| V <sub>OUT</sub>                                               |

| Output Short Circuit Duration Continuous                       |

| Power Dissipation PLCC 1000 mW                                 |

| (Derate at 10 mW/°C above +50°C)                               |

| $\theta_{JA}$ , Thermal Impedance $\hfill \ldots 80^\circ C/W$ |

| Operating Temperature Range                                    |

| Industrial (A Version)40°C to +85°C                            |

| Lead Temperature (Soldering 10 sec)+300°C                      |

| Vapour Phase (60 sec)+215°C                                    |

| Infrared (15 sec) +220°C                                       |

|                                                                |

\*This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADM5170 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

$\cap$

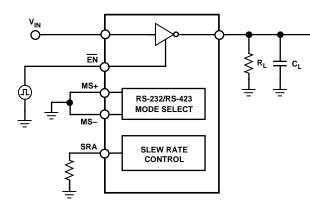

Figure 1. Timing Test Circuit

Figure 3. Enable/Disable Timing Waveforms

Figure 2. Rise/Fall Timing Waveforms

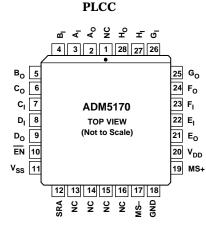

#### **PIN CONFIGURATION**

NC = NO CONNECT

#### **PIN FUNCTION DESCRIPTION**

| Mnemonic                     | Function                                                                                                                                                                             |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>              | Power Supply Input, +10 V $\pm$ 10%.                                                                                                                                                 |

| V <sub>ss</sub>              | Power Supply Input, $-10 \text{ V} \pm 10\%$ .                                                                                                                                       |

| GND                          | Ground Pin. Must be connected to 0 V.                                                                                                                                                |

| $A_{\rm I} \ldots H_{\rm I}$ | Digital Input to Drivers A to H.                                                                                                                                                     |

| $A_0 \dots H_0$              | RS-232/RS-423 Output from Drivers A to H.                                                                                                                                            |

| ĒN                           | Enable Pin. When high, all outputs are 3-stated.                                                                                                                                     |

| MS+, MS-                     | Mode Select Inputs. Used to control the output                                                                                                                                       |

|                              | level swing. With MS+ & MS- connected to GND, RS-423A output levels are selected. With MS+ connected to $V_{DD}$ and MS- connected to $V_{SS}$ , RS-232 output levels are developed. |

| SRA                          | Slew Rate Adjust Input. An external resistor (2 k $\Omega$ to 10 k $\Omega$ ) connected between this pin and GND is used to control the Output Slew Rate (10 V/µs to 2.2 V/µs).      |

#### **Slew Rate Programming**

The slew rate for the ADM5170 is controlled by a single resistor connected between the SRA pin and GND. The slew rate is approximately.

Slew Rate (V/

$$\mu s$$

) = 20/ $R_{SRA}$  ( $k\Omega$ )

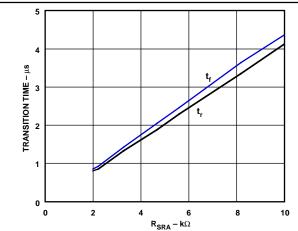

Resistors between 2 k $\Omega$  and 10 k $\Omega$  may be used providing a slew rate which may be varied from 10 V/µs to 2.2 V/µs. Figure 5 in the Typical Performance Characteristics section shows how the slew rate varies with  $R_{\rm SRA}$  while Figure 8 shows how the transition time (10% to 90%) varies with  $R_{\rm SRA}$ . Waveshaping of the output allows the user to control the level of interference (near-end crosstalk) which may be coupled to adjacent circuits in an interconnection. The recommended output characteristics for cable length and data rate are given in the EIA RS-423A specifications.

Maximum Data Rate (kB/s) = 300/t (for rates from 1 kB/s to 100 kB/s).

Cable Length (feet) =

$$100 X t$$

(Max Length =  $4000 ft$ .)

where *t* is the transition time (in  $\mu$ s) for the output to swing from 10% to 90% of its steady state values. The absolute maximum data rate is 100 kB/s and the maximum cable length is limited to 4000 ft.

#### **Output Mode Programming**

The ADM5170 has two programmable output modes which provide different output voltage levels. The low output mode meets the specifications of EIA standards RS-423A while the high output mode meets the RS-232 specifications. The high output mode provides greater output swings and is suitable for driving lines where higher attenuation levels must be tolerated. This mode is selected by connecting the mode select pins to the supplies, MS+ to  $V_{\rm DD}$  and MS- to  $V_{\rm SS}$ . The low output mode is selected by connecting both mode select pins MS+ and MS- to GND. This mode provides a controlled output swing with lower output levels.

|                 |                 | Outputs |      |                                    |

|-----------------|-----------------|---------|------|------------------------------------|

| MS+             | MS-             | EN      | Data | Output                             |

| GND             | GND             | 0       | 0    | 5 V to 6 V (RS-423)                |

| GND             | GND             | 0       | 1    | -5 V to -6 V (RS-423)              |

| V <sub>DD</sub> | V <sub>ss</sub> | 0       | 0    | $(V_{DD} - 3 V) (RS-232)^{1}$      |

| V <sub>DD</sub> | V <sub>ss</sub> | 0       | 1    | $(V_{SS}^{-1} + 3 V) (RS-232)^{1}$ |

| X               | X               | 1       | X    | High Z                             |

<sup>1</sup>Minimum Output Level.

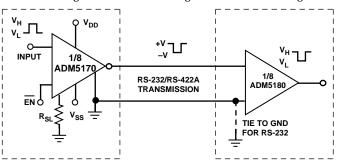

#### **Typical Application Circuit**

A typical application circuit using a single driver in the ADM5170 is shown in Figure 4. This circuit is suitable for either RS-232 or RS-423 communication. An ADM5180 octal receiver is used to translate the signal back to CMOS logic level at the receiving end.

Figure 4. RS-232/RS-423A Typical Application Circuit

Figure 5. Typical Slew Rate vs. R<sub>SRA</sub>

Figure 6. Slew Rate ( $R_{_{SRA}} = 2 \ k\Omega$ )

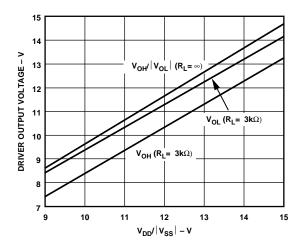

Figure 7.  $V_{OH}/V_{OL}$  vs.  $V_{DD}/V_{SS}$  (RS-232 Mode)

Figure 8. Typical Rise/Fall Times (RS-423A Mode) vs.  $R_{_{SRA}}$

|    |    |   | <br>   |        |   |

|----|----|---|--------|--------|---|

|    |    |   | $\geq$ |        |   |

|    |    | _ |        | $\geq$ | ļ |

| 5V |    |   |        |        |   |

|    | 5V |   |        |        |   |

Figure 9. Slew Rate ( $R_{_{SRA}} = 10 \ k\Omega$ )

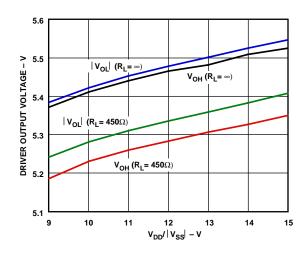

Figure 10.  $V_{OH}/V_{OL}$  vs.  $V_{DD}/V_{SS}$  (RS-423 Mode)

### ADM5170

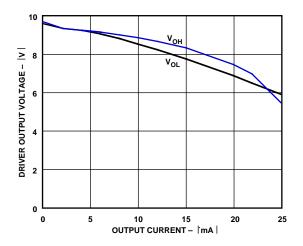

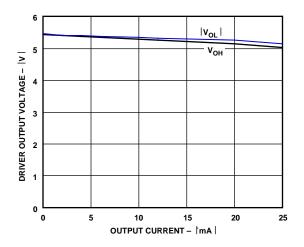

Figure 11. Driver Output Voltage vs. Output Current (RS-232 Mode)

Figure 12. Driver Output Voltage vs. Output Current (RS-423 Mode)

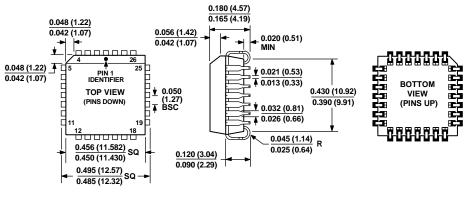

### **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-047-AB CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

> Figure 13. 28-Lead Plastic Leaded Chip Carrier [PLCC] (P-28) Dimensions shown in inches and (millimeters)

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                  | Package Option |

|--------------------|-------------------|------------------------------------------------------|----------------|

| ADM5170APZ         | –40°C to +85°C    | 28-Lead Plastic Leaded Chip Carrier [PLCC]           | P-28           |

| ADM5170APZ-REEL    | -40°C to +85°C    | 28-Lead Plastic Leaded Chip Carrier [PLCC], 13" Reel | P-28           |

<sup>1</sup> Z = RoHS Compliant Part.

### **REVISION HISTORY**

#### 9/2017-Rev. 0 to Rev. A

| Deleted 28-Lead Plastic DIP PackageUniversal                 |

|--------------------------------------------------------------|

| Changes to Features Section and General Description Section1 |

| Changes to Absolute Maximum Ratings Table                    |

| Deleted DIP Pin Configuration Figure4                        |

| Moved Ordering Guide                                         |

| Updated Outline Dimensions                                   |

| Changes to Ordering Guide7                                   |

10/1993—Revision 0: Initial Version

042508-A

Rev. A | Page 7 of 7