COMPLIANT

HALOGEN FREE

# 3 A Current Mode Constant On-Time Synchronous Buck Regulator

#### **DESCRIPTION**

The SiP12116 is a high frequency current-mode constant on-time (CM-COT) synchronous buck regulator with integrated high side and low side power MOSFETs. Its power stage is capable of supplying up to 3 A continuous current at 600 kHz switching frequency. This regulator produces an adjustable output voltage down to 0.6 V from 4.5 V to 15 V input rail to accommodate a variety of applications, including consumer electronics, computing, telecom, and industrial.

SiP12116's CM-COT architecture delivers ultrafast transient response and low ripple over the full load range with minimum output capacitance and no ESR requirements. The device features a built in soft start of 2.2 ms and integrated compensation.

The device also includes cycle-by-cycle current limit, over temperature protection (OTP) and input under voltage lockout (UVLO).

The SiP12116 is available in lead (Pb)-free 3 mm x 3 mm DFN10-33C lead package with thermal pad.

#### **FEATURES**

- 4.5 V to 15 V input voltage

- Adjustable output voltage down to 0.6 V

- 3 A continuous output current

- Integrated compensation

- 600 kHz switching frequency

- Ultrafast transient response

- < 5 μA typical shutdown current

- Cycle by cycle current limit

- · Power good function

- Fixed soft start: 2.9 ms, typ.

- Material categorization: for definitions of compliance please see <a href="https://www.vishav.com/doc?99912"><u>www.vishav.com/doc?99912</u></a>

#### **APPLICATIONS**

- · Graphics cards

- Set -top- box

- LCD TV

- Notebook computers

- HDD / SSD

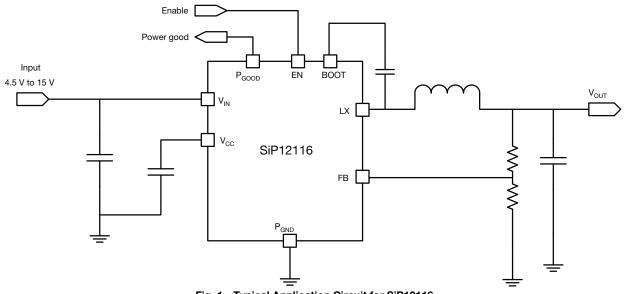

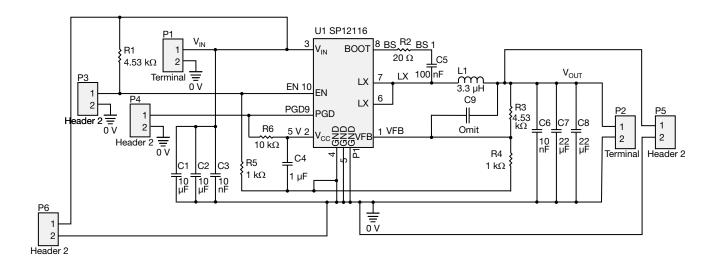

#### TYPICAL APPLICATION CIRCUIT AND PACKAGE OPTIONS

Fig. 1 - Typical Application Circuit for SiP12116

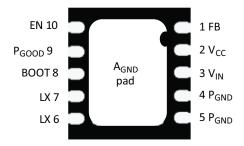

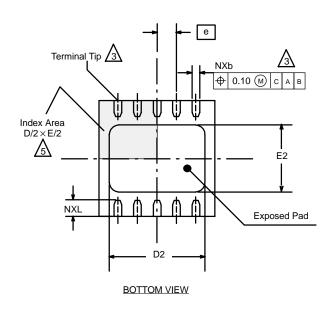

#### **PIN CONFIGURATION**

Fig. 2 - SiP12116 Pin Configuration (Bottom View)

| PIN CONFIGURATION |                  |                                                                                                                                     |  |  |  |  |  |

|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIN NUMBER        | NAME             | NAME FUNCTION                                                                                                                       |  |  |  |  |  |

| 1                 | FB               | Feedback voltage 0.6 V (typ.) input. Use a resistor divider between V <sub>OUT</sub> and thermal pad to set the output voltage      |  |  |  |  |  |

| 2                 | V <sub>CC</sub>  | Internal regulator output                                                                                                           |  |  |  |  |  |

| 3                 | V <sub>IN</sub>  | Input supply voltage for power MOS and regulator. V <sub>IN</sub> = 4.5 V to 15 V                                                   |  |  |  |  |  |

| 4, 5              | P <sub>GND</sub> | Power ground                                                                                                                        |  |  |  |  |  |

| 6, 7              | LX               | Switching node, inductor connection point                                                                                           |  |  |  |  |  |

| 8                 | воот             | Bootstrap pin - connect a capacitor of at least 100 nF from BOOT to LX to develop the floating supply for the high side gate driver |  |  |  |  |  |

| 9                 | $P_{GOOD}$       | Power good output. Open drain                                                                                                       |  |  |  |  |  |

| 10                | EN               | Enable input. Pull enable above 1.5 V to enable and below 0.4 V to disable the part. Do not float this pin                          |  |  |  |  |  |

| Pad               | A <sub>GND</sub> | Analog ground. The pad also improves thermal performance                                                                            |  |  |  |  |  |

| ORDERING INFORMATION |                  |                          |  |  |  |

|----------------------|------------------|--------------------------|--|--|--|

| PART NUMBER          | PACKAGE          | MARKING<br>(LINE 1: P/N) |  |  |  |

| SiP12116DMP-T1-GE4   | DFN10 3 x 3 2116 |                          |  |  |  |

| SiP12116DB           | Reference        | ce board                 |  |  |  |

#### **MARKING**

Format:

Line 1: Dot Line 2: P/N

Line 3: Siliconix Logo + ESD Symbol

Line 4: Factory Code + Year Code + Work Week Code + LOT Code

| ABSOLUTE MAXIMUM RATINGS                                   |                               |                                           |      |  |  |  |  |

|------------------------------------------------------------|-------------------------------|-------------------------------------------|------|--|--|--|--|

| ELECTRICAL PARAMETER                                       | CONDITIONS                    | LIMIT                                     | UNIT |  |  |  |  |

| V <sub>IN</sub>                                            | Reference to P <sub>GND</sub> | -0.3 to 16                                |      |  |  |  |  |

| V <sub>CC</sub>                                            | Reference to A <sub>GND</sub> | -0.3 to 6                                 |      |  |  |  |  |

| LX                                                         | Reference to P <sub>GND</sub> | -1 to 16                                  | ]    |  |  |  |  |

| L V (AC)                                                   | 100 ns                        | -2 to 17                                  | V    |  |  |  |  |

| LX (AC)                                                    | 10 ns                         | -6 to 17                                  |      |  |  |  |  |

| BOOT                                                       | Reference to P <sub>GND</sub> | -0.3 to V <sub>IN</sub> + V <sub>CC</sub> | 1    |  |  |  |  |

| All logic input and output (EN, FB, P <sub>GOOD</sub> )    | Reference to A <sub>GND</sub> | -0.3 to V <sub>CC</sub> + 0.3             | ]    |  |  |  |  |

| TEMPERATURE                                                |                               |                                           |      |  |  |  |  |

| Junction temperature                                       |                               | -40 to +150                               | °C   |  |  |  |  |

| Storage temperature                                        |                               | -65 to +150                               | ]    |  |  |  |  |

| POWER DISSIPATION                                          |                               |                                           |      |  |  |  |  |

| Junction-to-ambient thermal impedance (R <sub>thJA</sub> ) |                               | 36.3                                      | °C/W |  |  |  |  |

| ESD PROTECTION                                             |                               |                                           |      |  |  |  |  |

| Electronic discharge protection                            | НВМ                           | 2                                         | kV   |  |  |  |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE (all voltages referenced to GND = 0 V) |     |           |    |   |  |  |  |

|--------------------------------------------------------------------|-----|-----------|----|---|--|--|--|

| ELECTRICAL PARAMETER MINIMUM TYPICAL MAXIMUM UNIT                  |     |           |    |   |  |  |  |

| V <sub>IN</sub>                                                    | 4.5 | -         | 15 | V |  |  |  |

| V <sub>OUT</sub>                                                   | 0.6 | 0.6 - 5.5 |    |   |  |  |  |

| TEMPERATURE                                                        |     |           |    |   |  |  |  |

| Recommended ambient temperature -40 to +85                         |     |           |    |   |  |  |  |

| Operating junction temperature                                     | °C  |           |    |   |  |  |  |

www.vishay.com

# Vishay Siliconix

| DADAMETER                                   | OVALDOL                                        | TEST CONDITION                                   | LIMITS |             |      | UNIT |  |

|---------------------------------------------|------------------------------------------------|--------------------------------------------------|--------|-------------|------|------|--|

| PARAMETER                                   | SYMBOL                                         | $V_{IN}$ = 12 V, $T_A$ = -40 °C to +85 °C        | MIN.   | TYP.        | MAX. | UNII |  |

| POWER SUPPLY                                | <u> </u>                                       |                                                  |        |             |      |      |  |

| Input voltage                               | V <sub>IN</sub>                                |                                                  | 4.5    | -           | 15   | V    |  |

| V <sub>CC</sub> voltage                     | V <sub>CC</sub>                                |                                                  | -      | 5           | -    | ] v  |  |

| Input current                               | IV <sub>IN_NOLOAD</sub>                        | T <sub>A</sub> = 25 °C, non-switching, no load   | -      | 1.5         | -    | mA   |  |

| Shutdown current                            | IV <sub>IN_SHDN</sub>                          | EN = 0 V                                         | -      | 5           | 10   | μΑ   |  |

| V <sub>IN</sub> U <sub>VLO</sub> threshold  | $V_{IN\_UVLO}$                                 | Rising edge                                      | -      | 2.8         | -    | V    |  |

| V <sub>IN</sub> U <sub>VLO</sub> hysteresis | V <sub>IN_UVLO_HYS</sub>                       |                                                  | -      | 550         | -    | m۷   |  |

| CONTROLLER AND TIMING                       | <u>.                                      </u> |                                                  |        |             |      |      |  |

| Farabrahana                                 | V                                              | T <sub>A</sub> = 25 °C                           | 588    | 600         | 612  | mV   |  |

| Feedback voltage                            | V <sub>FB</sub>                                | T <sub>A</sub> = -40 °C to +85 °C                | 585    | 585 600 615 |      |      |  |

| V <sub>FB</sub> input bias current          | I <sub>FB</sub>                                |                                                  | -      | -           | 100  | n/   |  |

| On-time (600 kHz)                           | t <sub>ON</sub>                                | V <sub>IN</sub> = 12 V, (V <sub>OUT</sub> = 1 V) | -      | 138         | -    | ns   |  |

| Soft start timing                           |                                                |                                                  | 0.8    | -           | 5    | ms   |  |

| POWER MOSFETs                               |                                                |                                                  |        |             |      |      |  |

| High side on resistance                     | R <sub>ON_HS</sub>                             |                                                  | -      | 85          | 140  | mΩ   |  |

| Low side on resistance                      | R <sub>ON_LS</sub>                             | $V_{GS} = 5 \text{ V}$                           | -      | 55          | 105  |      |  |

| FAULT PROTECTIONS                           | <u>.                                      </u> |                                                  |        |             |      |      |  |

| Over current limit                          | I <sub>OCP</sub>                               | Inductor valley current, T <sub>A</sub> = 25 °C  | 3.6    | 4.25        | 5.1  | Α    |  |

| Over temperature pretection                 |                                                | Rising temperature                               | -      | 145         | -    | °C   |  |

| Over temperature protection                 |                                                | Hysteresis                                       | -      | 35          | -    |      |  |

| POWER GOOD                                  | <u>.                                      </u> |                                                  |        |             |      |      |  |

| Dower good output throughold                | V <sub>FB_RISING_VTH_OV</sub>                  | Rising (% V <sub>OUT</sub> ) -                   |        | 95          | -    | %    |  |

| Power good output threshold                 | V <sub>FB_FALLING_VTH_UV</sub>                 | Falling (% V <sub>OUT</sub> )                    | -      | -10         | -    | 7 %  |  |

| Power good pull low resistance              | R <sub>ON_PGOOD</sub>                          |                                                  | -      | 28          | 50   | Ω    |  |

| Power good delay Time                       | t <sub>DLY_PGOOD</sub>                         |                                                  | -      | 8           | -    | μs   |  |

| ENABLE THRESHOLD                            |                                                |                                                  |        |             | •    |      |  |

| Logic high level                            | V <sub>EN_H</sub>                              |                                                  | 1.5    | -           | -    | V    |  |

| Logic low level V <sub>EN_L</sub>           |                                                |                                                  | _      | _           | 0.4  | 7 V  |  |

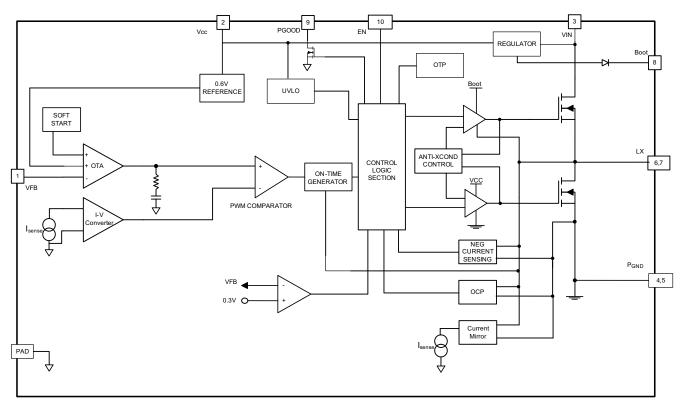

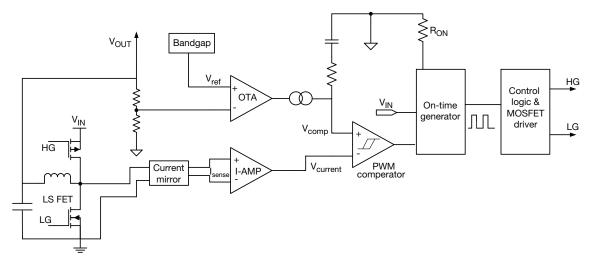

#### **FUNCTIONAL BLOCK DIAGRAM**

Fig. 3 - SiP12116 Functional Block Diagram

#### **ELECTRICAL CHARACTERISTICS**

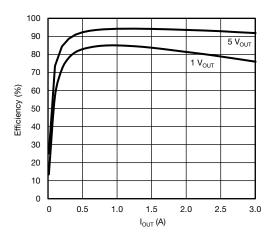

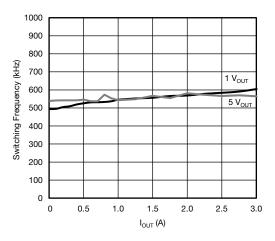

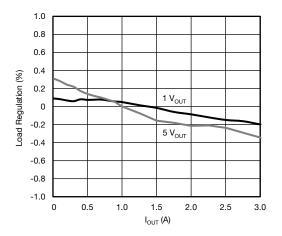

( $V_{IN}$  = 12 V,  $V_{OUT}$  = 1 V, L = 1.5  $\mu$ H, C = 3 x 22  $\mu$ F (ceramic), unless noted otherwise)

Fig. 4 - Efficiency vs. I<sub>OUT</sub>

Fig. 5 - Frequency Variation vs. I<sub>OUT</sub>

Fig. 6 - Load Regulation vs.  $I_{\text{OUT}}$

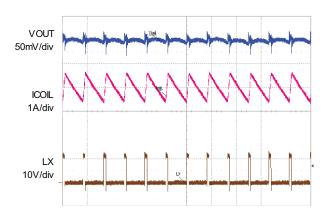

Fig. 7 - Steady-State,  $I_{OUT} = 3$  A, Time = 2  $\mu$ s/div

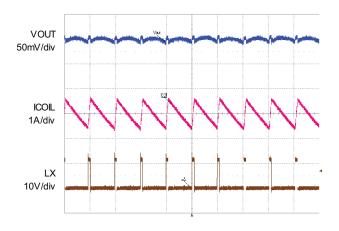

Fig. 8 - Steady-State,  $I_{OUT} = 0$  A, Time = 2  $\mu$ s/div

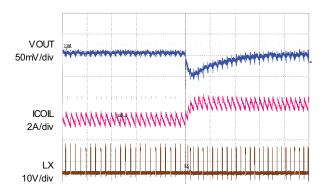

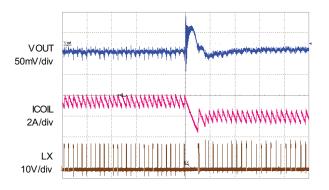

Fig. 9 - Load Step Undershoot Response, $I_{OUT} = 0$  A to 1.5 A, Time = 10  $\mu$ s/div

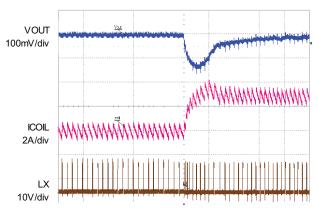

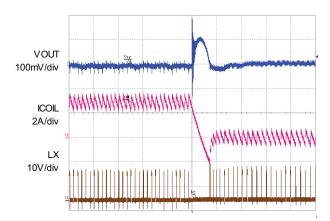

Fig. 10 - Load Step Undershoot Response,  $I_{OUT}$  = 0 A to 3 A, Time = 10  $\mu s/div$

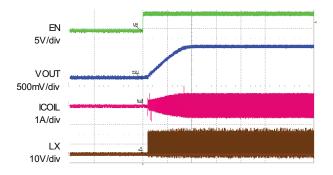

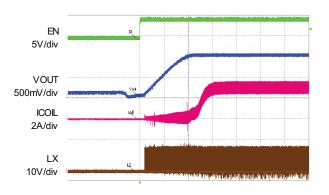

Fig. 11 - Start-Up,  $I_{OUT} = 0$  A, Time = 1  $\mu$ s/div

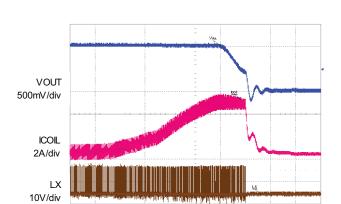

Fig. 12 - Load Step Overshoot Response, I<sub>OUT</sub> = 1.5 A to 0 A, Time = 10 µs/div

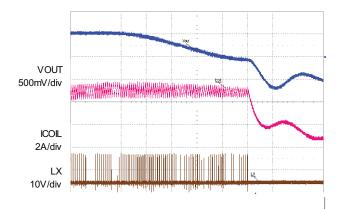

Fig. 13 - Load Step Overshoot Response,  $I_{OUT}$  = 3 A to 0 A, Time = 10  $\mu$ s/div

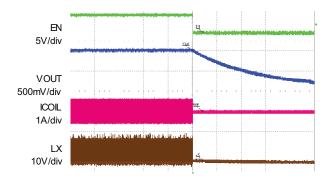

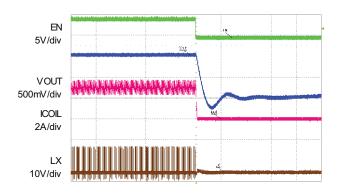

Fig. 14 - Shut-Down, I<sub>OUT</sub> = 0 A, Time = 200 ms/div

Fig. 15 - Load Step Undershoot Response I<sub>OUT</sub> = 0 A to 3 A, Time = 1 ms/div

Fig. 16 - Over Current Protection, I<sub>VALLEY</sub> = 4 A, Time =  $100 \mu s/div$

Fig. 17 - Shut-Down,  $I_{OUT}$  = 3 A, Time = 50  $\mu$ s/div

Fig. 18 - Over Current Protection,  $I_{VALLEY} = 4 A$ , Time = 20  $\mu$ s/div

#### **OPERATIONAL DESCRIPTION**

#### **Device Overview**

SiP12116 is a high efficiency monolithic synchronous buck regulator capable of delivering up to 3 A continuous current. The device has fixed switching frequency of 600 kHz. The control scheme is based on current - mode constant-on-time architecture, which delivers fast transient response and minimizes external components. Thanks to the internal current ramp information, no high ESR output bulk or virtual ESR network is required for the loop stability. SiP12116 has a full set of protection features:

- Cycle by cycle over current protection

- Over temperature protection with hysteresis

The device also features a dedicated enable pin for easy power sequencing and an open drain Power Good output.

The device is available in 3x3 DFN10 package with an exposed power pad to deliver high power density with ease of use.

#### **Power Stage**

SiP12116 integrates a high performance power stage with an 85 m $\Omega$  n-channel high side MOSFET and a 55 m $\Omega$  n-channel low side MOSFET. The MOSFETs are optimized to achieve up to 95 % efficiency at 600 kHz switching frequency.

The power input voltage  $(V_{IN})$  can go up to 15 V and down as low as 4.5 V for power conversion.

#### **PWM Control Mechanism**

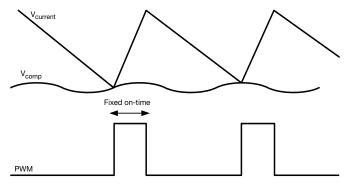

SiP12116 employs a state-of-the-art current - mode COT (CM-COT) control mechanism. During steady-state operation, output voltage is compared with internal reference (0.6 V typ.) and the amplified error signal ( $V_{comp}$ ) is generated. In the meantime, inductor valley current is sensed, and its slope ( $I_{sense}$ ) is converted into a voltage signal ( $V_{current}$ ) to be compared with  $V_{comp}$ . Once  $V_{current}$  is lower than  $V_{comp}$ , a single shot ON-time is generated for a fixed time set by an internal  $R_{ON}$ .

Figure 19 illustrates the basic block diagram for CM-COT architecture and Figure 20 demonstrates the basic operational principle:

Fig. 19 - CM-COT Block Diagram

Fig. 20 - CM-COT Operational Principle

#### **OUTPUT MONITORING AND PROTECTION FEATURES**

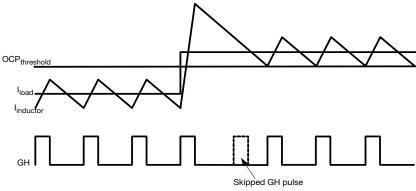

#### **Output Over Current Protection (OCP)**

SiP12116 has cycle by cycle over current limit control. The inductor valley current is monitored during LS FET turn-on period through  $R_{\rm DS(on)}$  sensing. After a pre-defined blanking time, the valley current is compared with internal threshold (4.25 A typ.) to determine the threshold for OCP. If the monitored current is higher than the internal threshold, HS turn-on pulse is skipped and LS FET is kept on until the valley current returns below OCP limit.

OCP is enabled immediately after  $V_{\text{IN}}$  passes UVLO level and enable is high.

In the figure below we see the ripple current riding on the DC load current. The valley current is calculated by taking one half the ripple current minus the DC load current.

For example if  $I_{OUT}=3$  A and ripple current = 1.2 A,  $I_{VALLEY}=3$  A - 0.6 A = 2.4 A. The typical DC full load current would be 4.85 A which is calculated by 4.25 A (OCP typ.) + 0.6 A. Here we see changing the ripple current (inductor value) can change the maximum DC load current value.

Fig. 21 - Over Current Protection Illustration

#### **Negative Current Protection**

Similar to the output over current protection, the negative current protection is realized by monitoring the current across the LS FET.

When the valley point of the inductor current reaches -2.5 A for first cycles, both HS and LS FETs are off.

#### Over Temperature Protection (OTP)

SiP12116 has internal thermal monitor block that turns off both HS and LS FETs when junction temperature is above 145 °C (typ.). A hysteresis of 35 °C is implemented, so when junction temperature drops below 110 °C, the device restarts by initiating soft-start sequence again.

#### **Soft Start**

SiP12116 has a built in soft-start function of  $\sim 2.2$  ms. Once  $V_{\text{IN}}$  is above UVLO level (3.33 V typ.),  $V_{\text{OUT}}$  will ramp up slowly, rising monotonically to the programmed output voltage.

#### **Pre-bias Startup**

In case of pre-bias startup, the output is monitored through the FB pin. If the sensed voltage on FB is higher than the internal reference ramp value, control logic prevents HS and LS FET from switching to avoid a negative output voltage spike due to LS FET turn on.

#### **Design Procedure**

The design process of the SiP12116 is quite straight forward. Only few passive components such as output capacitors and Inductor need to be selected.

The following paragraph describes the selection procedure for these peripheral components for a given operating conditions.

In the next example the following definitions apply:

V<sub>IN</sub> max.: the highest specified input voltage

$V_{\text{IN}}$  min.: the minimum effective input voltage subject to voltage drops due to connectors, fuses, switches, and PCB traces.

There are two values of load current to evaluate - continuous load current and peak load current.

Continuous load current relates to thermal stress considerations which drive the selection of the inductor and input capacitors.

Peak load current determines instantaneous component stresses and filtering requirements such as inductor saturation, output capacitors, and design of the current limit circuit.

The following specifications are used in this design:

- $V_{IN} = 12 V \pm 10 \%$

- $V_{OUT} = 1.2 \text{ V} \pm 1 \%$

www.vishay.com

## Vishay Siliconix

#### **Inductor Selection**

In order to determine the inductance, the ripple current must first be defined. Cost, PCB size, output ripple, and efficiency are all used in the selection process. Low inductor values result in smaller size and allow faster transient performance but create higher ripple current which can reduce efficiency. Higher inductor values will reduce the ripple current, and transient response. Efficiency especially at higher load currents will also be compromised due to the higher DCR (within a given case size).

The ripple current also sets the boundary for power-save operation. The switching regulator will typically enter power-save mode when the load current decreases to 1/2 of the ripple current. For example, if ripple current is 1 A then power-save operation will typically start at loads approaching 0.5 A. Alternatively, if ripple current is set at 40 % of maximum load current, then power-save will start for loads less than ~ 20 % of maximum current.

Setting the ripple current 20 % to 50 % of the maximum load current provides an optimal trade-off of the areas mentioned above.

This table provides a simple easy guide for setting up the board. If excessive jitter is noticed then reducing the inductor to the next standard value may be needed.

| SIP12116 CONFIGURATION LOOK UP TABLE |                         |                  |                            |                               |  |  |  |

|--------------------------------------|-------------------------|------------------|----------------------------|-------------------------------|--|--|--|

| V <sub>IN</sub><br>(V)               | V <sub>OUT</sub><br>(V) | INDUCTOR<br>(µH) | $R_{FB\_TOP}$ ( $\Omega$ ) | $R_{FB\_BOTTOM}$ ( $\Omega$ ) |  |  |  |

| 12                                   | 1                       | 1.5              | 4.53K                      | 6.81K                         |  |  |  |

| 12                                   | 3.3                     | 3.3              | 4.53K                      | 1K                            |  |  |  |

| 12                                   | 5                       | 3.3              | 4.53K                      | 619R                          |  |  |  |

| 5                                    | 1                       | 1.5              | 4.53K                      | 6.81K                         |  |  |  |

| 5                                    | 3.3                     | 1.5              | 4.53K                      | 1K                            |  |  |  |

The equation for determining inductance is shown next.

#### Example

In this example, the inductor ripple current is set equal to 30 % of the maximum load current. Thus ripple current will be 30 % x 3 A or 0.9 A. To find the minimum inductance needed, use the  $V_{\text{IN}}$  and  $t_{\text{ON}}$  values that correspond to  $V_{\text{IN}\,\text{max}}$ .

$$L = (V_{IN} - V_{OUT}) \times \frac{t_{ON}}{\Delta i}$$

Plugging numbers into the above equation we get

L = (13.2 V - 1.2 V) x

$$\frac{151 \times 10^{-9} \text{ s}}{0.9 \text{ A}}$$

= 2 µH

A smaller value of 1.5  $\mu H$  is selected which is a standard value. This will increase the maximum ripple current by 25 %.

Note that the inductor must be rated for the maximum DC load current plus 1/2 of the ripple current. The actual ripple current using the chosen 1  $\mu$ H inductor comes out to be.

$$\Delta i = (13.2 \text{ V} - 1.2 \text{ V}) \times \frac{151 \text{ ns}}{1.5 \text{ µH}} = 1.2 \text{ A}$$

#### **Output Capacitance Calculation**

The output capacitance is usually chosen to meet transient requirements. A worst-case load release, from maximum load to no load at the exact moment when inductor current is at the peak, determines the required capacitance. If the load release is instantaneous (load changes from maximum to zero in  $<1/f_{\text{sw}}$   $\mu\text{s}$ ), the output capacitor must absorb all the inductor's stored energy. This will approximately cause a peak voltage on the capacitor according to the following equation.

$$C_{OUT min.} = \frac{L \times (I_{OUT} + \frac{1}{2} \times I_{RIPPLE max.})^2}{(V_{PEAK})^2 - (V_{OUT})^2}$$

Assuming a peak voltage  $V_{PEAK}$  of 1.3 V (100 mV rise upon load release), and a 3 A load release, the required capacitance is shown by the next equation.

$$C_{OUT \text{ min.}} = \frac{1.5 \ \mu\text{H x } (3 \ \text{A} + 0.5 \ \text{x} \ (1.2 \ \text{A})^2}{(1.3 \ \text{V})^2 - (1.2 \ \text{V})^2} = 77.8 \ \mu\text{F}$$

If the load release is relatively slow, the output capacitance can be reduced.

Using MLCC ceramic capacitors we will use 3 x 22  $\mu$ F or 66  $\mu$ F as the total output capacitance.

#### **Switching Frequency Variations**

The switching frequency variation in COT can be mainly attributed to the increase in conduction losses as the load increases. Since the on time is constant the controller must account for losses and maintain output regulation by reducing the off time. Hence the  $f_{\text{sw}}$  tends to increase with load

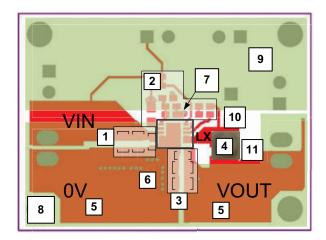

#### LAYOUT CONSIDERATIONS

The SiP12116 offers the designer a small part count, 3 A buck regulator solution. If the below layout recommendations are followed, the same layout can be used to cover a wide range of output currents and voltages without any changes to the board design and only minor changes to the component values in the schematic.

The reference design has a majority of the components placed on the top layer. This allows for easy assembly and straightforward layout.

Figure 22 outlines the pointers for the layout considerations and the explanations follow.

Fig. 22 - Reference Design Pointers

Place input ceramic capacitors close to the voltage input pins with a small 10 nF / 100 nF placed as close as the design rules will allow. This will help reduce the size of the input high frequency current loop and consequently reduce the high frequency ripple noise seen at the input and the LX node.

- Place the setup and control passive devices logically around the IC with the intention of placing a quiet ground plane beneath them on a secondary layer.

- 3. It is advisable to use ceramic capacitors at the output to reduce impedance. Place these as close to the IC  $P_{GND}$  and output voltage node as design will allow. Place a small 10 nF / 100 nF ceramic capacitor closest to the IC and inductor loop.

- 4. The loop between LX, V<sub>OUT</sub> and the IC P<sub>GND</sub> should be as compact as possible. This will lower series resistance and also make the current loop smaller enabling the high frequency response of the output capacitors to take effect.

- The output impedance should be small when high current is required; use high current traces, multiple layers can be used with many vias if the design allows.

- Use many vias when multiple layers are involved. This will have the effect of lowering the resistance between layers and reducing the via inductance of the PCB nets.

- The quiet A<sub>GND</sub> should be connected to the P<sub>GND</sub> plane near to the input GND at one connection only of at least 1 mm width.

- 8. P<sub>GND</sub> can be used on internal layers if the resistance of the PCB is to be small; this will also help remove heat. Use extra vias if needed but be mindful to allow a path between the vias.

- A quiet plane should be employed for the A<sub>GND</sub>, this is placed under the small signal passives. This can be placed on multiple layers if needed for heat removal.

- 10. The LX copper can also be used on a single or multiple layers, use a number of vias to stitch the layers.

- 11. The copper area beneath the inductor has been removed (on all layers) in this design to reduce the inductive coupling that occurs between the inductor and the GND trace. No other voltage planes should be placed under this area.

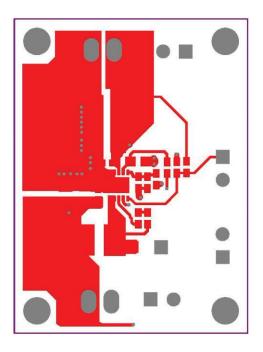

Fig. 23 - Top Layer

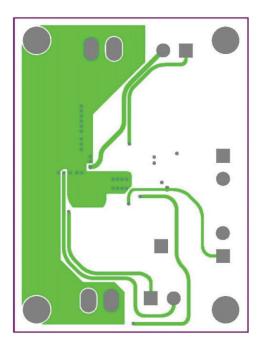

Fig. 24 - Inner Layer 2

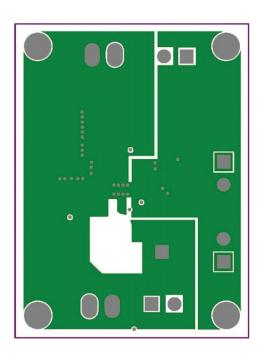

Fig. 25 - Inner Layer 1

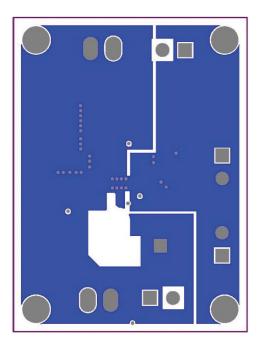

Fig. 26 - Bottom Layer

| BILL ( | <b>BILL OF MATERIAL</b> $V_{IN} = 12 \text{ V}$ , $V_{OUT} = 3.3 \text{ V}$ , $f_{SW} = 600 \text{ kHz}$ |                |                  |         |         |                      |                 |  |  |

|--------|----------------------------------------------------------------------------------------------------------|----------------|------------------|---------|---------|----------------------|-----------------|--|--|

| ITEM   | QTY                                                                                                      | REFERENCE      | PCB<br>FOOTPRINT | VALUE   | VOLTAGE | PART NUMBER          | MANUFACTURER    |  |  |

| 1      | 2                                                                                                        | C1, C2         | 1210             | 10 μF   | 35 V    | C1210C106M6PACTU     | Kemet           |  |  |

| 2      | 2                                                                                                        | C3, C6         | 0402             | 10 nF   | 50 V    | GRM155R71H103KA88D   | Murata          |  |  |

| 3      | 1                                                                                                        | C4             | 0603             | 1 μF    | 10 V    | C0402C105M8PACTU     | Kemet           |  |  |

| 4      | 1                                                                                                        | C5             | 0402             | 100 nF  | 35 V    | CGA2B3X7R1V104K050BB | Vishay          |  |  |

| 5      | 2                                                                                                        | C7, C8         | 0805             | 22 µF   | 10 V    | CL21A226MPQNNNE      | Samsung         |  |  |

| 6      | 1                                                                                                        | R2             | 0402             | 20 ΩR   | -       | CRCW040220R0FKED     | Vishay          |  |  |

| 7      | 1                                                                                                        | R3             | 0402             | 4.53 kΩ | -       | CRCW04024K53FKED     | Vishay          |  |  |

| 8      | 1                                                                                                        | R4             | 0402             | 1 kΩ    | -       | CRCW0402249KFKED     | Vishay          |  |  |

| 9      | 1                                                                                                        | L1             | IHLP2525         | 3.3 µH  | -       | IHLP2020BZER3R3M01   | Vishay          |  |  |

| 10     | 1                                                                                                        | U1             | DFN10-3x3        | -       | -       | SiP12116             | Vishay          |  |  |

| 11     | 1                                                                                                        | R1             | 0402             | 4.53 kΩ | -       | CRCW04024K53FKED     | Vishay          |  |  |

| 12     | 1                                                                                                        | R5             | 0402             | 1 kΩ    | -       | CRCW0402249KFKED     | Vishay          |  |  |

| 13     | 1                                                                                                        | R6             | 0402             | 10 kΩ   | -       | CRCW040210K0FKED     | Vishay          |  |  |

| 14     | 4                                                                                                        | P3, P4, P5, P6 | HDR1x2           | -       | -       | 90120-0126           | Vishay          |  |  |

| 15     | 2                                                                                                        | P1, P2         | TERM2            | -       | -       | 282834-2             | TE Connectivity |  |  |

www.vishay.com

# Vishay Siliconix

| PRODUCT SUMMARY               |                                                                                     |

|-------------------------------|-------------------------------------------------------------------------------------|

| Part number                   | SiP12116                                                                            |

| Description                   | 3 A, 4.5 V to 15 V input, current mode constant on-time, synchronous buck regulator |

| Input voltage min. (V)        | 4.5                                                                                 |

| Input voltage max. (V)        | 15                                                                                  |

| Output voltage min. (V)       | 0.6                                                                                 |

| Output voltage max. (V)       | 5.5                                                                                 |

| Continuous current (A)        | 3                                                                                   |

| Switch frequency min. (kHz)   | 600                                                                                 |

| Switch frequency max. (kHz)   | 600                                                                                 |

| Pre-bias operation (yes / no) | Yes                                                                                 |

| Internal bias reg. (yes / no) | No                                                                                  |

| Compensation                  | Integrated                                                                          |

| Enable (yes / no)             | Yes                                                                                 |

| P <sub>GOOD</sub> (yes / no)  | Yes                                                                                 |

| Overcurrent protection        | Fixed                                                                               |

| Protection                    | OCP, OTP, UVLO                                                                      |

| Light load mode               | n/a                                                                                 |

| Peak efficiency (%)           | 95                                                                                  |

| Package type                  | DFN10-33C                                                                           |

| Package size (W, L, H) (mm)   | 3 x 3 x 0.9                                                                         |

| Status code                   | 2                                                                                   |

| Product type                  | microBUCK (step down regulator)                                                     |

| Applications                  | Computing, consumer, networking                                                     |

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package / tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg?62969">www.vishay.com/ppg?62969</a>.

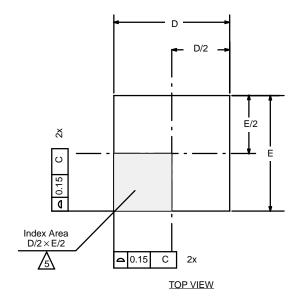

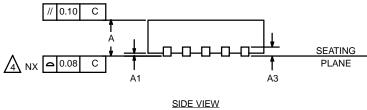

### **DFN-10 LEAD (3 X 3)**

#### NOTES:

1. All dimensions are in millimeters and inches.

2. N is the total number of terminals.

Dimension b applies to metallized terminal and is measured between 0.15 and 0.30 mm from terminal tip.  $\,$

Coplanarity applies to the exposed heat sink slug as well as the terminal.

The pin #1 identifier may be either a mold or marked feature, it must be located within the zone iindicated.

|                                              | МІ                               | LLIMETE  | RS   | INCHES    |           |       |

|----------------------------------------------|----------------------------------|----------|------|-----------|-----------|-------|

| Dim                                          | Min                              | Nom      | Max  | Min       | Nom       | Max   |

| Α                                            | 0.80                             | 0.90     | 1.00 | 0.031     | 0.035     | 0.039 |

| A1                                           | 0.00                             | 0.02     | 0.05 | 0.000     | 0.001     | 0.002 |

| А3                                           |                                  | 0.20 BSC |      |           | 0.008 BSC |       |

| b                                            | 0.18                             | 0.23     | 0.30 | 0.007     | 0.009     | 0.012 |

| D                                            |                                  | 3.00 BSC |      | 0.118 BSC |           |       |

| D2                                           | 2.20                             | 2.38     | 2.48 | 0.087     | 0.094     | 0.098 |

| Е                                            |                                  | 3.00 BSC |      | 0.118 BSC |           |       |

| E2                                           | 1.49                             | 1.64     | 1.74 | 0.059     | 0.065     | 0.069 |

| е                                            | 0.50 BSC                         |          |      |           | 0.020 BSC |       |

| L                                            | 0.30 0.40 0.50 0.012 0.016 0.020 |          |      |           |           |       |

| *Use millimeters as the primary measurement. |                                  |          |      |           |           |       |

| ECN: S-42134—Rev. A, 29-Nov-04<br>DWG: 5943  |                                  |          |      |           |           |       |

Document Number: 73181 www.vishay.com 29-Nov-04 sww.vishay.com

# **Legal Disclaimer Notice**

Vishay

## **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.