# Three-Channel Interleaved CCM PFC Controller

#### Description

The FAN9673 is an interleaved three-channel Continuous Conduction Mode (CCM) Power Factor Correction (PFC) controller IC intended for PFC pre-regulators. Incorporating circuits for the implementation of leading edge, average current, and "boost"-type power factor correction, the FAN9673 enables the design of a power supply that fully complies with the IEC1000-3-2 specification. Interleaved operation provides substantial reduction in the input and output ripple currents and the conducted EMI filtering becomes easier and cost effective.

An innovative channel management function allows slave channels to be loaded and unloaded smoothly in lower power–level conditions according to setting voltage on the CM pin, improving the PFC converter's load transient response.

The FAN9673 also incorporates a variety of protection functions, including: peak current limiting, input voltage brownout protection, and TriFault Detect function.

### Features

- Continuous Conduction Mode Control

- Three–Channel PFC Control (Maximum)

- Average Current-Mode Control

- PFC Slave Channel Management Function

- Programmable Operation Frequency Range: 18 kHz ~ 40 kHz or 55 kHz ~ 75 kHz

- Programmable PFC Output Voltage

- Dual Current Limit Functions

- TriFault Detect Protects Against Feedback Loop Failure

- Sag Protection

- Programmable Soft–Start

- Under-Voltage Lockout (UVLO)

- Differential Current Sensing

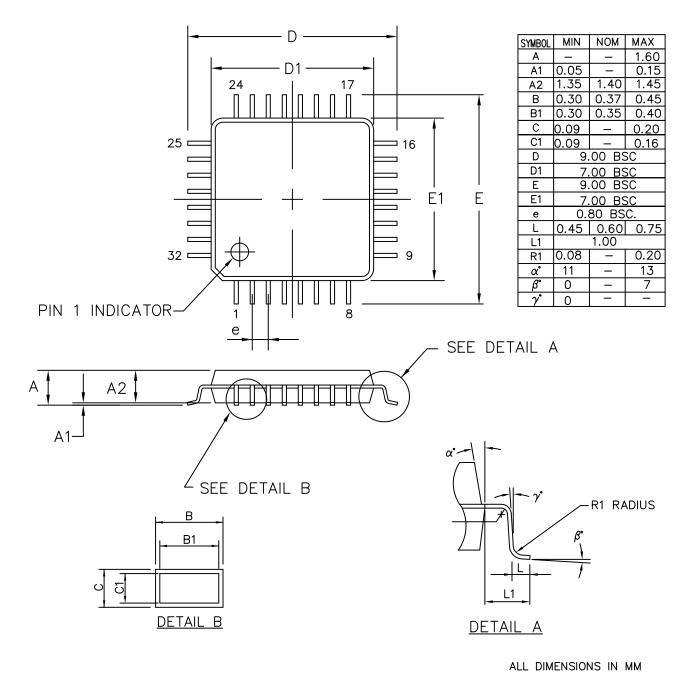

- Available in 32-Pin LQFP Package

### **Typical Applications**

- High Power AC-DC Power Supply

- DC Motor Power Supply

- White Goods; e.g. Air Conditioner Power Supply

- Server and Telecom Power Supply

- Industrial Welding and Power Supply

### **ON Semiconductor®**

www.onsemi.com

LQFP32 CASE 561AB

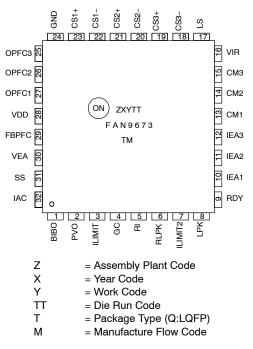

### MARKING DIAGRAM

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

### **ORDERING INFORMATION**

| Part Number | Operating<br>Temperature Range | Package                                                 | Packing Method |

|-------------|--------------------------------|---------------------------------------------------------|----------------|

| FAN9673Q    | –40°C to 105°C                 | 32LD, LQFP, JEDEC MS-026, Variation BBA, 7 mm<br>Square | Tray           |

| FAN9673QX   |                                | oquale                                                  | Tape & Reel    |

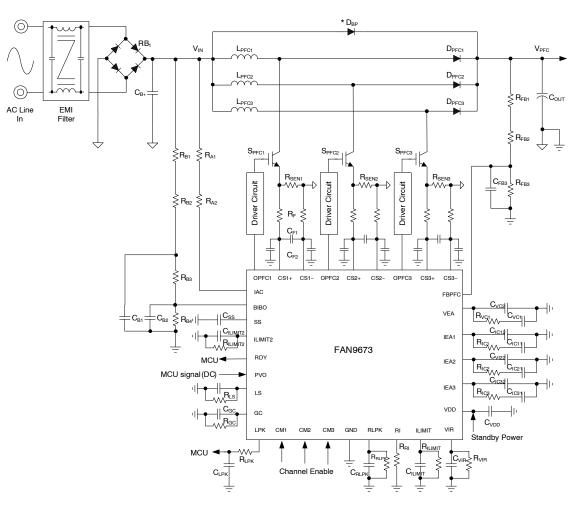

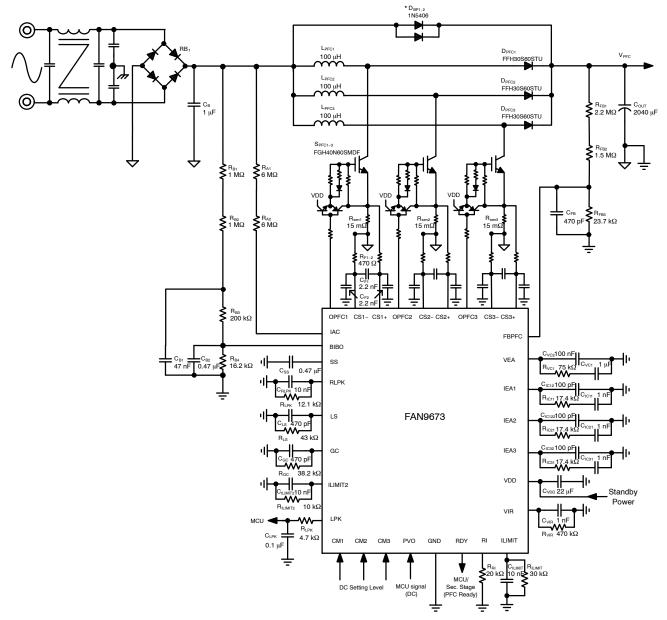

### TYPICAL APPLICATION

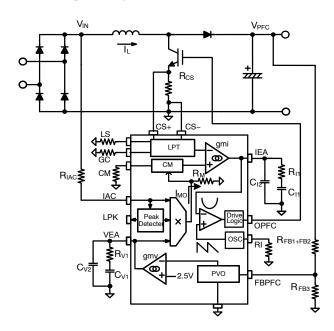

\* About D<sub>BP</sub> please reference System Design Precautions

Figure 1. Typical Application Diagram for Three-Channel PFC Converter

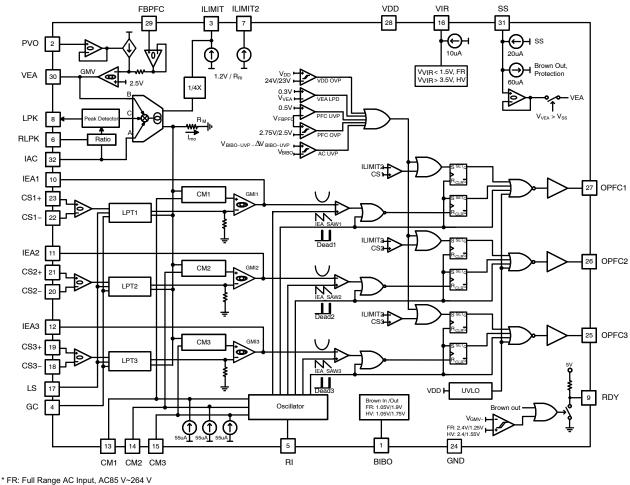

### **BLOCK DIAGRAM**

HV: High Voltage Range AC Input, AC180 ~ 264 V

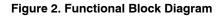

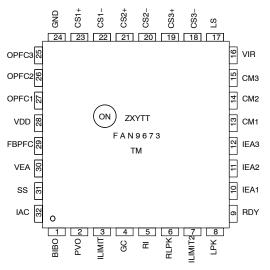

### **PIN CONFIGURATION**

Figure 3. Pin Layout (Top View)

#### Table 1. PIN DEFINITIONS

| Pin # | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | BIBO    | Brown In/Out Level Setting: This pin is used for brown in/out setting.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2     | PVO     | Programmable Output Voltage: DC voltage from a microcontroller (MCU) can be applied to this pin to program the output voltage level. The operation range is $3.5 \text{ V} \sim 0.5 \text{ V}$ . If V <sub>PO</sub> < $0.5 \text{ V}$ , the PVO function is disabled.                                                                                                                                                                                                               |

| 3     | ILIMIT  | Current Command Clamp Setting: Average current mode is to control average value of inductor current by a current command. Connecting a resistor and a capacitor to this pin can determine a limit value of the current command.                                                                                                                                                                                                                                                     |

| 4     | GC      | Input Voltage Gain Control: Connecting a resistor on this pin to set a gain on the input–voltage signal to match FBPFC. The signal here is used for the LPT function. A small capacitor connecting from GC to GND is recommended for noise filtering.                                                                                                                                                                                                                               |

| 5     | RI      | Oscillator Setting: There are two oscillator frequency ranges: 18 ~ 40 kHz and 50 ~ 75 kHz. A resistor connected from RI to ground determines the switching frequency. A resistor value between 10.6 k ~44.4 k $\Omega$ is recommended.                                                                                                                                                                                                                                             |

| 6     | RLPK    | Ratio of V <sub>LPK</sub> and V <sub>IN</sub> : Connect a resistor and a capacitor to this pin to adjust the ratio of V <sub>IN</sub> peak to V <sub>LPK</sub> . Typical value is 12.4 k $\Omega$ (1:100 of V <sub>LPK</sub> and V <sub>IN</sub> peak). The accuracy of V <sub>LPK</sub> is primarily determined by the tolerance of R <sub>RLPK</sub> at this pin.                                                                                                                 |

| 7     | ILIMIT2 | Peak Current Limit Setting: Connect a resistor and a capacitor to this pin to set the over-current limit threshold and to protect power devices from damage due to inductor saturation. This pin sets the over-current threshold for cycle-by-cycle current limit.                                                                                                                                                                                                                  |

| 8     | LPK     | Peak of Line Voltage: This pin can be used to provide information about the peak amplitude od the line voltage to an MCU.                                                                                                                                                                                                                                                                                                                                                           |

| 9     | RDY     | Output Ready Signal: When the feedback voltage on FBPFC exceeds 2.4 V, the RDY pin outputs a high-state $V_{RDY}$ signal to inform the MCU the downstream power stage can start normal operation. If AC brownout is detected, the $V_{RDY}$ signal is LOW to signal the MCU the PFC is not ready.                                                                                                                                                                                   |

| 10    | IEA1    | Output 1 of PFC Current Amplifier: The signal from this pin is compared with an internal sawtooth signal to determine the pulse width for PFC gate drive 1.                                                                                                                                                                                                                                                                                                                         |

| 11    | IEA2    | Output 2 of PFC Current Amplifier: The signal from this pin is compared with an internal sawtooth signal to determine the pulse width for PFC gate drive 2.                                                                                                                                                                                                                                                                                                                         |

| 12    | IEA3    | Output 3 of PFC Current Amplifier: The signal from this pin is compared with an internal sawtooth signal to determine the pulse width for PFC gate drive 3.                                                                                                                                                                                                                                                                                                                         |

| 13    | CM1     | Channel 1 Management Setting: This pin is used to configure the characteristics of PFC enable/<br>disable. Pull voltage on this pin LOW (= 0 V) to enable and HIGH (> 4 V) to disable the whole PFC system.                                                                                                                                                                                                                                                                         |

| 14    | CM2     | Channel 2 Management Setting: There are two control methods for channel 2. The first uses an external signal to enable/disable channel 2 ( $V_{CM2} = 0 V/V_{CM2} > 4 V$ ). The second is linear increase/decrease loading of channel 2 when $V_{VEA}$ , proportional to power level, meets the setting level on $V_{CM2}$ .                                                                                                                                                        |

| 15    | CM3     | Channel 3 Management Setting: Same as the CM2 pin, but for Channel 3.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16    | VIR     | Input Voltage Range Setting: A capacitor and a resistor are connected in parallel from this pin to GND. When $V_{VIR} > 3.5$ V, the PFC controller only works for the high–voltage input range (180 $V_{AC} \sim 264$ $V_{AC}$ ) and $R_{IAC}$ must be 12 M $\Omega$ . When $V_{VIR} < 1.5$ V, the PFC controller works for the Universal Input voltage range (90 $V_{AC} \sim 264$ $V_{AC}$ ) and $R_{IAC}$ must be 6 M $\Omega$ . Voltage between 1.5 V and 3.5 V is not allowed. |

| 17    | LS      | Setting for Current Predict Function: A resistor, connected from this pin to ground, is used to adjust the compensation of linear predict function (LPT). A small capacitor connected from this pin to GND is recommended for noise filtering.                                                                                                                                                                                                                                      |

| 18    | CS3-    | Channel 3 Negative PFC Current Sense Input                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 19    | CS3+    | Channel 3 Positive PFC Current Sense Input                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 20    | CS2-    | Channel 2 Negative PFC Current Sense Input                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21    | CS2+    | Channel 2 Positive PFC Current Sense Input                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 22    | CS1-    | Channel 1 Negative PFC Current Sense Input                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 23    | CS1+    | Channel 1 Positive PFC Current Sense Input                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24    | GND     | Ground Reference and Return                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 25    | OPFC3   | Channel 3 PFC Gate Drive: The totem-pole output drive for the MOSFET or IGBT. This pin has an internal 15 V clamp to protect the external power switch.                                                                                                                                                                                                                                                                                                                             |

#### Table 1. PIN DEFINITIONS (continued)

| Pin # | Name  | Description                                                                                                                                                              |

|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26    | OPFC2 | Channel 2 PFC Gate Drive: The totem-pole output drive for the MOSFET or IGBT. This pin has an internal 15 V clamp to protect the external power switch.                  |

| 27    | OPFC1 | Channel 1 PFC Gate Drive: The totem-pole output drive for the MOSFET or IGBT. This pin has an internal 15 V clamp to protect the external power switch.                  |

| 28    | VDD   | External Bias Supply for the IC: The typical turn-on and turn-off threshold voltages are 12.8 V and 10.8 V respectively.                                                 |

| 29    | FBPFC | Voltage Feedback Input for PFC: Inverting input of the PFC error amplifier. This pin is connected to the PFC output through a resistor-divider network.                  |

| 30    | VEA   | Output of PFC Voltage–Loop Amplifier: An error–amplifier output for the PFC voltage feedback loop. A compensation network is connected between this pin and ground.      |

| 31    | SS    | Soft–Start: Connect a capacitor to this pin to set the soft–start time. Pulling this pin to ground can disable the gate drive outputs OPFC1, OPFC2 and OPFC3.            |

| 32    | IAC   | Input AC Current: During normal operation, this input provides a current reference for an internal gain modulator. The recommended maximum current on IAC is 65 $\mu$ A. |

#### ABSOLUTE MAXIMUM RATINGS (T<sub>J</sub> = 25°C unless otherwise noted)

| Symbol                | Para                                                                              | meter                                            | Min  | Мах                     | Unit |

|-----------------------|-----------------------------------------------------------------------------------|--------------------------------------------------|------|-------------------------|------|

| V <sub>DD</sub>       | DC Supply Voltage                                                                 |                                                  |      | 30                      | V    |

| V <sub>OPFC</sub>     | Voltage on OPFC1, OPFC2, OPFC3 I                                                  | Pins                                             | -0.3 | V <sub>DD</sub> + 0.3 V | V    |

| VL                    | Voltage on IAC, BIBO, LPK RLPK, FE<br>CS1-, CS2-, CS3-, CM1, CM2, CM3<br>VIR Pins |                                                  | -0.3 | 7.0                     | V    |

| V <sub>IEA</sub>      | Voltage on IEA1, IEA2, IEA3, SS Pins                                              | ;                                                | 0    | 8                       | V    |

| I <sub>IAC</sub>      | Input AC Current                                                                  |                                                  |      | 1<br>0.5                |      |

| I <sub>PFC-OPFC</sub> | Peak PFC OPFC Current, Source or S                                                | Sink                                             |      | 0.5                     | A    |

| PD                    | Power Dissipation, $T_A < 50 \ ^\circ C$                                          |                                                  |      | 1640                    | mW   |

| $R_{\thetaJ-A}$       | Thermal Resistance (Junction-to-Air)                                              |                                                  |      | 77                      | °C/W |

| TJ                    | Operating Junction Temperature                                                    |                                                  | -40  | 150                     | °C   |

| T <sub>STG</sub>      | Storage Temperature Range                                                         |                                                  | -55  | 150                     | °C   |

| ΤL                    | Lead temperature (Soldering)                                                      |                                                  |      | 260                     | °C   |

| ESD                   | Electrostatic Discharge Capability                                                | Human Body Model,<br>ANSI/ESDA/JEDEC JS-001-2012 |      | 4                       | kV   |

|                       |                                                                                   | Charged Device Model,<br>JESD22-C101             |      | 2                       |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                | Parameter               | Min | Тур | Max | Unit |

|-----------------------|-------------------------|-----|-----|-----|------|

| V <sub>DD-OP</sub>    | Operating Voltage       |     | 15  |     | V    |

| L <sub>MISMATCH</sub> | Boost Inductor Mismatch | -5  |     | +5  | %    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond All voltage values, except differential voltage, are given with respect to GND pin.

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

## **ELECTRICAL CHARACTERISTICS** (Unless otherwise noted, $V_{DD}$ = 15 V and $T_{J}$ = -40~105°C)

| Symbol                     | Parameter                                                                      | Condition                                                                   | Min  | Тур  | Max  | Unit |

|----------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| VDD SECTIO                 | N                                                                              |                                                                             |      |      |      |      |

| I <sub>DD ST</sub>         | Startup Current                                                                | $V_{DD} = V_{TH-ON} - 0.1 V$                                                |      | 30   | 80   | μA   |

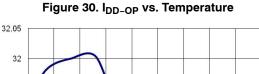

| I <sub>DD-OP</sub>         | Operating Current                                                              | $V_{DD}$ = 14 V, Output Not Switching, $R_{RI}$ = 25 k $\Omega$             | 4    | 6    | 7    | mA   |

| V <sub>TH-ON</sub>         | Turn-On Threshold Voltage                                                      | V <sub>DD</sub> Rising                                                      | 11.7 | 12.8 | 13.9 | V    |

| $\Delta V_{TH}$            | UVLO Hysteresis                                                                |                                                                             | 2    |      | 3    | V    |

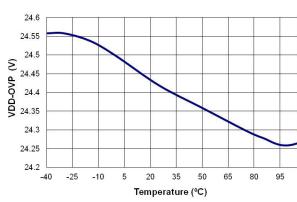

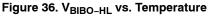

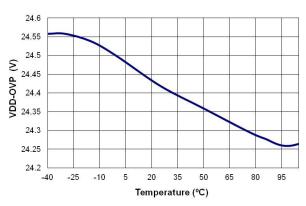

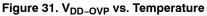

| V <sub>DD-OVP</sub>        | V <sub>DD</sub> OVP Threshold                                                  | OPFC1~3 Disabled, IEA1~3 and SS Pull Low                                    | 23   | 24   | 25   | V    |

| $\Delta V_{\text{DD-OVP}}$ | V <sub>DD</sub> OVP Hysteresis                                                 |                                                                             |      | 1    |      | V    |

| t <sub>D-OVP</sub>         | V <sub>DD</sub> OVP Debounce Time                                              |                                                                             |      |      | 80   | μs   |

| OSCILLATOF                 | R (Note 3)                                                                     |                                                                             | -    | -    | -    |      |

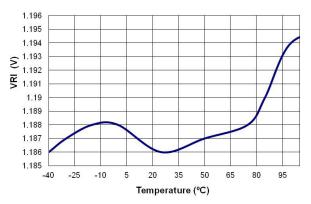

| V <sub>RI</sub>            | Sourcing Voltage on RI                                                         | $R_{RI} = 25 \text{ k}\Omega$                                               | 1.15 | 1.20 | 1.25 | V    |

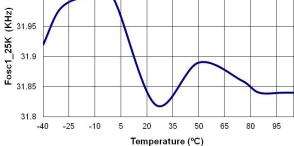

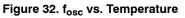

| f <sub>OSC1</sub>          | PFC Frequency Test Case 1                                                      | R <sub>RI</sub> = 25 kΩ                                                     | 30   | 32   | 34   | kHz  |

| f <sub>OSC2</sub>          | PFC Frequency Test Case 2                                                      | R <sub>RI</sub> = 12.5 kΩ                                                   | 58   | 62   | 66   | kHz  |

| f <sub>DV</sub>            | Voltage Stability                                                              | $13 \text{ V} \leq \text{V}_{DD} \leq 22 \text{ V}$                         |      |      | 2    | %    |

| f <sub>DT</sub>            | Temperature Stability                                                          |                                                                             |      |      | 2    | %    |

| $\Delta V_{IEA-SAW32}$     | VIEA-SAW of PFC Frequency 32 kHz                                               | R <sub>RI</sub> = 25 kΩ                                                     |      | 5    |      | V    |

| $\Delta V_{IEA-SAW64}$     | VIEA-SAW of PFC Frequency 64 kHz                                               | R <sub>RI</sub> = 12.5 kΩ                                                   |      | 5.15 |      | V    |

| D <sub>PFC-MAX</sub>       | Maximum Duty Cycle                                                             | V <sub>IEA</sub> > 7 V                                                      | 94   | 97   |      | %    |

| D <sub>PFC-MIN</sub>       | Minimum Duty Cycle                                                             | V <sub>IEA</sub> < 1 V                                                      |      |      | 0    | %    |

| f <sub>RANGE1</sub>        | Frequency Range 1 (Notes 3, 4)                                                 |                                                                             | 18   |      | 40   | kHz  |

| f <sub>RANGE2</sub>        | Frequency Range 2 (Notes 3, 4)                                                 |                                                                             | 55   |      | 75   | kHz  |

| t <sub>DEAD-MIN</sub>      | Minimum Dead Time                                                              | R <sub>RI</sub> = 10.7 kΩ                                                   |      | 600  |      | ns   |

| INPUT-RANG                 | GE SETTING (VIR)                                                               | •                                                                           |      |      |      |      |

| V <sub>VIR-H</sub>         | HIGH Setting Level for High Voltage In-<br>put Range                           | $R_{VIR} = 500 \text{ k}\Omega \text{ (V}_{VIR} = 5 \text{ V)}$             | 3.5  |      |      | V    |

| $V_{VIR-L}$                | LOW Setting Level for Low Voltage In-<br>put Range or Full Voltage Input Range | V <sub>VIR</sub> = 0 V                                                      |      |      | 1.5  | V    |

| I <sub>VIR</sub>           | Sourcing Current of VIR Pin                                                    |                                                                             | 7    | 10   | 13   | μA   |

| PFC SOFT-S                 | TART                                                                           | •                                                                           |      |      |      |      |

| I <sub>SS</sub>            | Constant Current Output for Soft-Start                                         | System Brown-in                                                             |      | 22   |      | μA   |

| V <sub>SS</sub>            | Maximum Voltage on SS                                                          |                                                                             | 6.8  |      |      | V    |

| I <sub>SS-Discharge</sub>  | Discharge Current of SS Pin                                                    | Brownout, SAG, V <sub>CM1</sub> > 4 V, R <sub>RI</sub> Open /<br>Short, OTP |      | 60   |      | μA   |

| VOLTAGE ER                 | ROR AMPLIFIER                                                                  | •                                                                           |      |      |      |      |

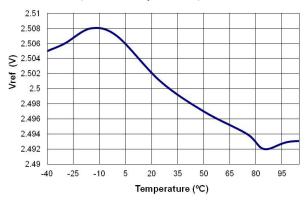

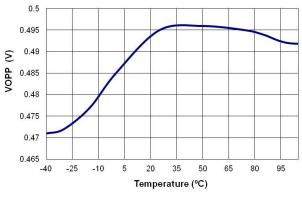

| V <sub>REF</sub>           | Reference Voltage                                                              | PVO = GND, $T_J = 25^{\circ}C$                                              | 2.45 | 2.50 | 2.55 | V    |

| A <sub>V</sub>             | Open-Loop Gain (Note 3)                                                        |                                                                             | 42   | 65   |      | dB   |

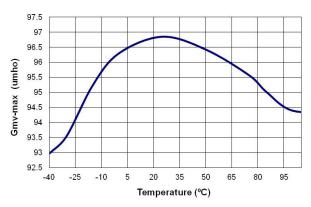

| G <sub>mv</sub>            | Transconductance                                                               | $V_{NONINV} - V_{INV} = 0.5 \text{ V}, \text{ T}_{J} = 25^{\circ}\text{C}$  |      | 100  | 1    | μS   |

| I <sub>FBPFC-L</sub>       | Maximum Source Current                                                         | V <sub>FBPFC</sub> = 2 V, V <sub>VEA</sub> = 3 V                            | 40   | 50   | 1    | μA   |

| I <sub>FBPFC-H</sub>       | Maximum Sink Current                                                           | V <sub>FBPFC</sub> = 3 V, V <sub>VEA</sub> = 3 V                            |      | -50  | -40  | μA   |

| I <sub>BS</sub>            | Input Bias Current Range                                                       |                                                                             | -1   |      | 1    | μA   |

| I <sub>FBPFC-FL</sub>      | Pull High Current for FBPFC                                                    | FBPFC Floating                                                              |      | 500  | 1    | nA   |

| V <sub>VEA-H</sub>         | Output High Voltage on V <sub>VEA</sub>                                        | V <sub>FBPFC</sub> = 2 V                                                    | 5.7  | 6.0  | 1    | V    |

| V <sub>VEA-L</sub>         | Output Low Voltage on V <sub>VEA</sub>                                         | V <sub>FBPFC</sub> = 3 V                                                    |      | 0    | 0.15 | V    |

### **ELECTRICAL CHARACTERISTICS** (Unless otherwise noted, $V_{DD}$ = 15 V and $T_{J}$ = -40~105°C)

| Symbol               | Parameter                                      | Condition                                                                                 | Min | Тур | Max | Unit |

|----------------------|------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| VOLTAGE EF           | RROR AMPLIFIER                                 |                                                                                           |     |     |     |      |

| I <sub>VEA-DIS</sub> | Discharge Current                              | Brownout, R <sub>RI</sub> Open /Short, OTP, SAG                                           |     | 10  |     | μA   |

| V <sub>VEA-OFF</sub> | Threshold Voltage for Low-Power De-<br>tection | When $V_{VEA}$ < $V_{VEA-OFF},$ $V_{OPFC1\sim3}$ are Off & $V_{IEA1\sim3}$ are Pulled Low |     | 0.3 |     | V    |

#### CURRENT ERROR AMPLIFIERS

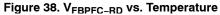

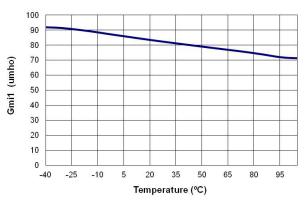

| G <sub>mi</sub>      | Transconductance            | $\label{eq:VNONINV} \begin{split} V_{NONINV} &= V_{INV}, \ V_{IEA} = 4 \ V, \\ V_{ILIMIT} &> 0.6 \ V, \ T_J = 25^\circ C \end{split}$                                     |     | 88  |     | μS |

|----------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| V <sub>OFFSET</sub>  | Input Offset Voltage        | $ \begin{array}{l} V_{VEA} = 0.45 \; V, \; R_{IAC} = 12 \; M\Omega, \\ V_{IAC} = 311 \; V, \; V_{FBPFC} = 2 \; V, \\ V_{VIR} > 5 \; V, \; T_J = 25^{\circ}C \end{array} $ |     | 0   |     | mV |

| $V_{IEA-H}$          | Output High Voltage         |                                                                                                                                                                           | 6.8 | 7.0 |     | V  |

| $V_{IEA-L}$          | Output Low Voltage          |                                                                                                                                                                           |     | 0   | 0.4 | V  |

| ۱ <sub>L</sub>       | Sourcing Current            |                                                                                                                                                                           | 35  | 50  |     | μΑ |

| Ι <sub>Η</sub>       | Sinking Current             | $\label{eq:VNONINV} \begin{array}{l} V_{NONINV} - V_{INV} = -0.6 \ V, \\ V_{IEA} = 6.5 \ V, \ V_{ILIMIT} > 0.6 \ V \end{array}$                                           |     | -50 | -35 | μΑ |

| A <sub>I</sub>       | Open-Loop Gain (Note 3)     |                                                                                                                                                                           | 40  | 50  |     | dB |

| I <sub>IEA-LOW</sub> | IEA Pin Pull-Low Capability | $V_{IEA} \ge 5 V$                                                                                                                                                         | 500 |     |     | μA |

#### GAIN MODULATOR (Current Command Generator)

| I <sub>AC</sub> | Input for AC Current (Notes 3, 5)                                       | Multiplier Linear Range                                                                                                                                                                                                | 0 |       | 65 | μA  |

|-----------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|----|-----|

| BW              | Bandwidth (Notes 3, 5)                                                  | I <sub>AC</sub> = 40 μA                                                                                                                                                                                                |   | 2     |    | kHz |

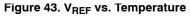

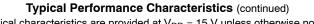

| V <sub>RM</sub> | Gain Modulator Output (I <sub>MO</sub> * R <sub>M</sub> ) Test<br>Cases |                                                                                                                                                                                                                        |   | 0.490 |    | V   |

|                 |                                                                         |                                                                                                                                                                                                                        |   | 0.430 |    |     |

|                 |                                                                         |                                                                                                                                                                                                                        |   | 0.327 |    |     |

|                 |                                                                         | $ \begin{array}{l} V_{IAC} = 311.13 \ V, \ R_{IAC} = 12 \ M\Omega, \ V_{FBPFC} = \\ 2.25 \ V, \ V_{BIBO} = 2 \ V, \ V_{CM2}, \ V_{CM3} > 4.5 \ V, \\ V_{VIR} > 3.5 \ V, \ T_J = 25^\circ C \end{array} $               |   | 0.320 |    |     |

|                 |                                                                         | $ \begin{array}{l} V_{IAC} = 373.35 \; V, \; R_{IAC} = 12 \; M\Omega, \; V_{FBPFC} = \\ 2.25 \; V, \; V_{BIBO} = 2 \; V, \; V_{CM2}, \; V_{CM3} > 4.5 \; V, \\ V_{VIR} > 3.5 \; V, \; T_{J} = 25^\circ C \end{array} $ |   | 0.260 |    |     |

| R <sub>M</sub>  | Resistor of Gain Modulator Output                                       | $R_{M} = V_{RM} / I_{MO}$                                                                                                                                                                                              |   | 7.5   |    | kΩ  |

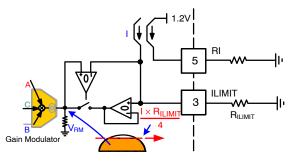

#### ILIMIT (Current Command Limit)

| V <sub>RM-R</sub>      | Range of Peak Value in Current Com-<br>mand (V <sub>ILIMIT</sub> /4) |                               | 0.2 |       | 0.8 | V  |

|------------------------|----------------------------------------------------------------------|-------------------------------|-----|-------|-----|----|

| V <sub>RM-ILIMIT</sub> | Current Command Limit Test Case                                      |                               |     | 0.504 |     | V  |

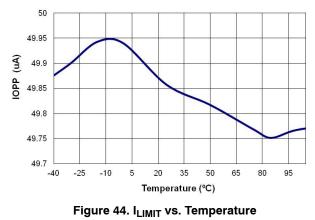

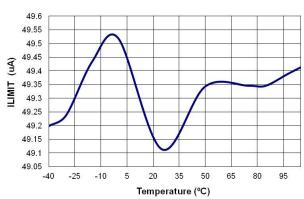

| I <sub>ILIMIT</sub>    | Sourcing Current of ILIMIT Pin                                       | $R_{RI} = 25 \text{ k}\Omega$ |     | 49    |     | μA |

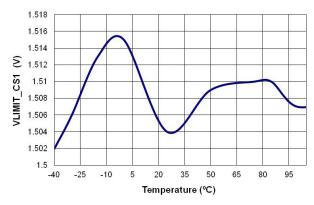

### ILIMIT2 (CS1 /CS2 /CS3, Pulse-by-Pulse Current Limit)

| V <sub>ILIMIT2-CS1</sub> | Peak Current Limit Voltage Test Case | $R_{\text{ILIMIT2}} = 30 \text{ k}\Omega, R_{\text{RI}} = 25 \text{ k}\Omega,$ | 1.48 | V  |

|--------------------------|--------------------------------------|--------------------------------------------------------------------------------|------|----|

| V <sub>ILIMIT2-CS2</sub> |                                      | CS1~3 > V <sub>ILIMIT2</sub><br>OPFC1 Disables, V <sub>IEA1~3</sub> Pull Low   | 1.48 | V  |

| V <sub>ILIMIT2-CS3</sub> |                                      |                                                                                | 1.48 | V  |

| I <sub>ILIMIT2</sub>     | Sourcing Current for ILIMIT2 Pin     | $R_{RI}$ = 25 kΩ, $T_J$ = 25°C                                                 | 49.5 | μA |

### **ELECTRICAL CHARACTERISTICS** (Unless otherwise noted, $V_{DD}$ = 15 V and $T_J$ = -40~105°C)

| Symbol                    | Parameter                                               | Condition                                               | Min | Тур | Max | Unit |  |  |

|---------------------------|---------------------------------------------------------|---------------------------------------------------------|-----|-----|-----|------|--|--|

| ILIMIT2 (CS1              | ILIMIT2 (CS1 /CS2 /CS3, Pulse-by-Pulse Current Limit)   |                                                         |     |     |     |      |  |  |

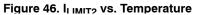

| t <sub>PFC-BNK1</sub>     | Leading–Edge Blanking Time of ILIMIT<br>of Each Channel | V <sub>DD</sub> = 15 V, OPFC Drops to 9 V               |     | 250 |     | ns   |  |  |

| t <sub>PFC-BNK2</sub>     | or Each Ghanner                                         |                                                         |     | 250 |     | ns   |  |  |

| t <sub>PFC-BNK3</sub>     |                                                         |                                                         |     | 250 |     | ns   |  |  |

| t <sub>PD1</sub>          | Propagation Delay to Output of Each<br>Channel          |                                                         |     | 200 | 400 | ns   |  |  |

| t <sub>PD2</sub>          | Channel                                                 |                                                         |     | 200 | 400 | ns   |  |  |

| t <sub>PD3</sub>          |                                                         |                                                         |     | 200 | 400 | ns   |  |  |

| V <sub>ILIMIT2-OPEN</sub> | Threshold of ILIMIT2 Open–Circuit Pro-<br>tection       | <code>OPFC1~3</code> Disabled and $V_{IEA1~3}$ Pull Low | 3.8 | 4.0 | 4.2 | V    |  |  |

#### TriFault Detect<sup>TM</sup>

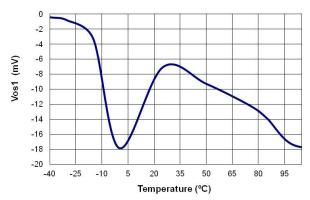

| V <sub>PFC-UVP</sub>    | FBPFC Under-Voltage Protection            |                                                                   | 0.4  | 0.5  | 0.6  | V  |

|-------------------------|-------------------------------------------|-------------------------------------------------------------------|------|------|------|----|

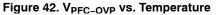

| V <sub>PFC-OVP</sub>    | FBPFC Over-Voltage Protection (OVP)       |                                                                   | 2.70 | 2.75 | 2.80 | V  |

| $\Delta V_{PFC-OVP}$    | FBPFC OVP                                 |                                                                   | 200  | 250  | 300  | mV |

| t <sub>FBPFC-OPEN</sub> | FBPFC Open Delay (Note 3)                 | $V_{FBPFC} = V_{PFC-UVP}$ to FBPFC Open, 470 pF from FBPFC to GND |      | 2    |      | ms |

| t <sub>FBPFC-UVP</sub>  | Under-Voltage Protection Debounce<br>Time |                                                                   |      | 50   |      | μs |

#### PVO

| V <sub>PVO</sub>           | Programmable Output Setting Range on PVO Pin |                                           | 0.3 |       | 3.5 | V  |

|----------------------------|----------------------------------------------|-------------------------------------------|-----|-------|-----|----|

| V <sub>PVO_DIS</sub>       | PVO Disable Voltage                          | PVO< V <sub>PVO_DIS</sub>                 |     | 0.2   |     | V  |

| V <sub>PVO-CLAMPH</sub>    | Low-clamp of FBPFC based on PVO              | FBPFC Connected to VEA, $V_{PVO}$ = 4 V   |     | 1.6   |     | V  |

| V <sub>FBPFC1</sub>        | FBPFC Voltage Test Cases                     | FBPFC Connected to VEA, $V_{PVO}$ = 0.3 V |     | 2.425 |     | V  |

| V <sub>FBPFC2</sub>        |                                              | FBPFC Connected to VEA, $V_{PVO}$ = 3.5 V |     | 1.625 |     | V  |

| I <sub>PVO-Discharge</sub> | PVO Discharge Current                        | PVO Open                                  |     | 1     |     | μA |

#### GAIN COMPENSATION (GC) SECTION (Note 6)

| I <sub>GC-L1</sub>   | Test Cases of Mirror Current of I <sub>AC</sub> on<br>GC Pin | $V_{VIR}$ = 0 V, $V_{IAC}$ = 127.28 V, $R_{IAC}$ = 6 $M\Omega,$  |      | 20.71 |      | μA |

|----------------------|--------------------------------------------------------------|------------------------------------------------------------------|------|-------|------|----|

| I <sub>GC-L2</sub>   |                                                              | $V_{VIR}$ = 0 V, $V_{IAC}$ = 311.13 V, $R_{IAC}$ = 6 $M\Omega,$  |      | 51.86 |      | μA |

| I <sub>GC-HV</sub>   |                                                              | $V_{VIR}$ = 5 V, $V_{IAC}$ = 311.13 V, $R_{IAC}$ = 12 $M\Omega.$ |      | 51.86 |      | μA |

| I <sub>GC-OPEN</sub> | Pull High Current for GC–Pin Open                            |                                                                  |      | 100   |      | nA |

| V <sub>GC-OPEN</sub> | GC-Pin Open Voltage                                          | $V_{GC} > V_{GC-OPEN} V_{IEA}$ , OPFC1, 2, 3 Blanking            | 2.85 | 3.00  | 3.15 | V  |

### INDUCTANCE SETTING (LS) SECTION (Note 6)

| R <sub>LS</sub> | Acceptable Range of Inductance Setting                                      |                              | 12 |    | 87 | kΩ |

|-----------------|-----------------------------------------------------------------------------|------------------------------|----|----|----|----|

| $V_{LS-MIN}$    | Voltage Difference between $V_{\mbox{FBPFC}}$ and $V_{\mbox{GC}}$ on LS Pin | $V_{FBPFC} - V_{GC} \ge 0 V$ |    | 50 |    | mV |

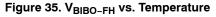

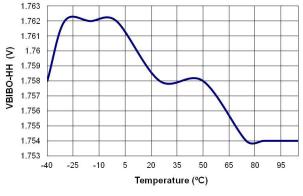

#### **BROWN IN /OUT**

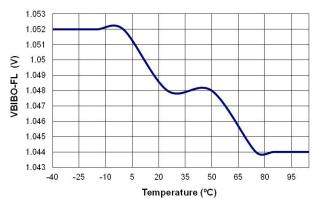

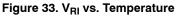

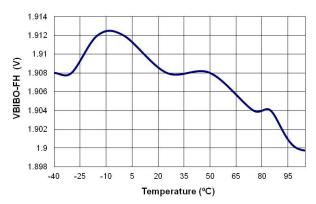

| V <sub>BIBO-FL</sub> | Threshold of Brown-out at VIR=LOW<br>Setting (Full AC-Input Range) | $V_{VIR}$ < 1.5 V, $R_{IAC}$ = 6 M $\Omega$                         | 1.00 | 1.05 | 1.10 | V  |

|----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|------|------|------|----|

| ΔV <sub>BIBO-F</sub> | Hysteresis                                                         | $V_{BIBO} > V_{BIBO-FL}+\Delta V_{BIBO-F}$ ,<br>Brown-in, Start SS  |      | 850  |      | mV |

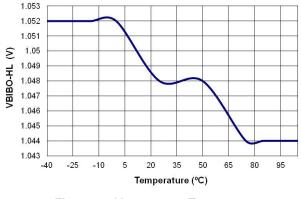

| V <sub>BIBO-HL</sub> | Threshold of BO at VIR=HIGH Setting<br>(High AC-Input Range)       | V <sub>VIR</sub> > 3.5 V, R <sub>IAC</sub> = 12 MΩ                  | 1.00 | 1.05 | 1.10 | V  |

| $\Delta V_{BIBO-H}$  | Hysteresis                                                         | $V_{BIBO} > V_{BIBO-HL} + \Delta V_{BIBO-H},$<br>Brown-in, Start SS |      | 700  |      | mV |

| t <sub>UVP</sub>     | Under-Voltage Protection Delay Time                                |                                                                     |      | 450  |      | ms |

### **ELECTRICAL CHARACTERISTICS** (Unless otherwise noted, $V_{DD}$ = 15 V and $T_J$ = -40~105°C)

| Symbol              | Parameter              | Condition                                                                                                        | Min | Тур  | Max | Unit |  |

|---------------------|------------------------|------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|--|

| SAG PROTE           | SAG PROTECTION SECTION |                                                                                                                  |     |      |     |      |  |

| V <sub>SAG</sub>    | SAG Voltage of BIBO    | 1. $V_{BIBO}$ < $V_{SAG}$ & $V_{RDY}$ High for 33 ms, or<br>2. $V_{BIBO}$ < $V_{SAG}$ & $V_{RDY}$ Low, Brownout, |     | 0.85 |     | V    |  |

| t <sub>SAG-DT</sub> | SAG Debounce Time      | $V_{BIBO}$ < $V_{SAG}$ & $V_{RDY}$ High                                                                          |     | 33   |     | ms   |  |

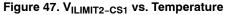

#### RLPK, VOLTAGE-SETTING RESISTANCE FOR PEAK DETECTOR

| I <sub>RLPK-OPEN</sub> | Pull High Current for RLPK Open                  |           |      | 100  |      | nA |

|------------------------|--------------------------------------------------|-----------|------|------|------|----|

| V <sub>RLPK-OPEN</sub> | Threshold of RLPK-pin Open-Circuit<br>Protection | RLPK Open | 2.28 | 2.40 | 2.52 | V  |

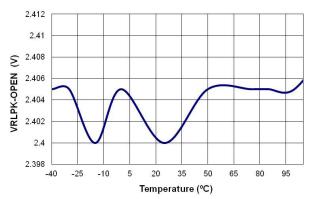

#### LPK, PEAK-DETECTOR OUTPUT (Note 7)

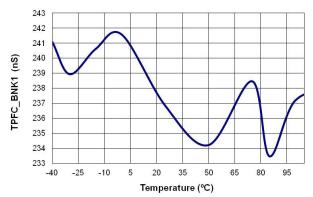

| V <sub>LPK-H1</sub> | V <sub>LPK</sub> Output Test Cases | $ \begin{array}{l} V_{IAC} = 311 \; V, \; R_{IAC} = 1 \; 2M\Omega, \\ V_{VIR} > 3.5 \; V, \; R_{LPK} = 12.4 \; k\Omega, \\ T_J = 25^{\circ} C \end{array} $                                                                                  | 3.168                                  | V |

|---------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---|

| V <sub>LPK-H2</sub> |                                    | $ \begin{array}{l} {\sf V}_{\rm IAC} = 373 \; {\sf V}, \; {\sf R}_{\rm IAC} = 12 \; {\sf M}\Omega, \\ {\sf V}_{\rm VIR} > 3.5 \; {\sf V}, \; {\sf R}_{\rm LPK} = 12.4 \; {\sf k}\Omega, \\ {\sf T}_{\rm J} = 25^{\circ}{\rm C} \end{array} $ | 3.80                                   | V |

| V <sub>LPK-L1</sub> |                                    |                                                                                                                                                                                                                                              | 1.29                                   | V |

| V <sub>LPK-L2</sub> |                                    | $ \begin{array}{l} {\sf V}_{\rm IAC} = 373 \; {\sf V}, \; {\sf R}_{\rm IAC} = 6 \; {\sf M}\Omega, \\ {\sf V}_{\rm VIR} < 1.5 \; {\sf V}, \; {\sf R}_{\rm LPK} = 12.4 \; {\sf k}\Omega, \\ {\sf T}_{\rm J} = 25^{\circ}{\rm C} \end{array} $  | 3.80                                   | V |

| V <sub>AC-OFF</sub> | AC OFF Threshold Voltage Test Case | $V_{IAC}$ = 373 V, $R_{IAC}$ = 12 MΩ, $V_{VIR}$ > 3.5V After $t_{AC-OFF}$ $V_{IEA}$ Pull Low                                                                                                                                                 | 32                                     | V |

| V <sub>AC-ON</sub>  | AC ON Threshold Voltage Test Case  | $V_{IAC}$ = 373 V, $R_{IAC}$ = 12 MΩ, $V_{VIR}$ > 3.5 V                                                                                                                                                                                      | V <sub>AC-OF</sub><br><sub>F</sub> +26 | V |

### CM1 SECTION

| I <sub>CM1</sub>         | CM1 Sourcing Current    |                                                                                                      |     | 55  |     | μA |

|--------------------------|-------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| V <sub>CM1-disable</sub> | PFC Disable Voltage     | I <sub>CM1</sub> * R <sub>CM1</sub> > 4 V<br>OPFC1~3 Disabled and IEA1~3 Pull Low<br>and SS Pull Low |     | 4   |     | V  |

| θ1                       | Phase of OPFC1          | When $I_{CM1} \star R_{CM1} < 4 V$ or Short                                                          |     | 0   |     | 0  |

| θ2                       | Phase of OPFC2 (Note 8) |                                                                                                      | 110 | 120 | 130 | 0  |

| <b>θ3</b>                | Phase of OPFC3 (Note 8) |                                                                                                      | 230 | 240 | 250 | 0  |

**CM2 SECTION**

| I <sub>CM2</sub>         | CM2 Sourcing Current      |                                                                                |     | 55  |     | μA |

|--------------------------|---------------------------|--------------------------------------------------------------------------------|-----|-----|-----|----|

| V <sub>CM2-disable</sub> | Channel-2 Disable Voltage | $I_{CM2} * R_{CM2} > 4 V$ or CM2 Floating<br>OPFC2 Disables and IEA2 Pulls Low |     | 4   |     | V  |

| V <sub>CM2-range</sub>   | Set VEA Unload Voltage    |                                                                                | 0   |     | 3.8 | V  |

| θ1                       | Phase of OPFC1 (Note 8)   | $I_{CM2} * R_{CM2} > 4 V \text{ or CM2 Floating}$                              |     | 0   |     | 0  |

| θ <b>3</b>               | Phase of OPFC3 (Note 8)   |                                                                                | 170 | 180 | 190 | 0  |

#### **CM3 SECTION**

| I <sub>CM3</sub>         | CM3 Output Current        |                                                                                |     | 55  |     | μA |

|--------------------------|---------------------------|--------------------------------------------------------------------------------|-----|-----|-----|----|

| V <sub>CM3-disable</sub> | Channel-3 Disable Voltage | $I_{CM3} * R_{CM3} > 4 V$ or CM3 Floating<br>OPFC3 Disables and IEA3 Pulls Low |     | 4   |     | V  |

| V <sub>CM3-range</sub>   | Set VEA Unload Voltage    |                                                                                | 0   |     | 3.8 | V  |

| θ1                       | Phase of OPFC1 (Note 8)   | When $I_{CM3} * R_{CM3} > 4 V$ or CM3 Floating                                 |     | 0   |     | 0  |

| θ2                       | Phase of OPFC2 (Note 8)   |                                                                                | 170 | 180 | 190 | 0  |

### **ELECTRICAL CHARACTERISTICS** (Unless otherwise noted, $V_{DD}$ = 15 V and $T_J$ = -40~105°C)

| Symbol               | Parameter                                    | Condition                                               | Min | Тур  | Max | Unit |

|----------------------|----------------------------------------------|---------------------------------------------------------|-----|------|-----|------|

| RDY SECTIO           | N                                            |                                                         |     |      |     |      |

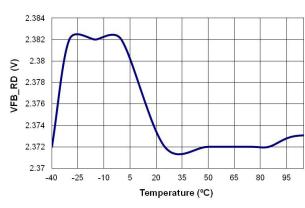

| V <sub>FB-RD</sub>   | Level of V <sub>FBPFC</sub> to Pull RDY High | $V_{PVO}$ = 0 V, Brown-in, $V_{FBPFC}$ > $V_{FB-RD}$    | 2.3 | 2.4  | 2.5 | V    |

| $\Delta V_{FB-RD-L}$ | Hysteresis                                   | $V_{PVO} = 0 \text{ V}, V_{IR} < 1.5 \text{ V}$         |     | 1.15 |     | V    |

| $\Delta V_{FB-RD-H}$ | Hysteresis                                   | $V_{PVO} = 0 \text{ V}, \text{ V}_{IR} > 3.5 \text{ V}$ |     | 0.85 |     | V    |

| Z <sub>RDY</sub>     | Pull High Input Impedance                    | $T_J = 25^{\circ}C$                                     |     | 100  |     | kΩ   |

| $V_{RDY-High}$       | HIGH Voltage of RDY                          |                                                         | 4.8 | 5.0  |     | V    |

| V <sub>RDY-Low</sub> | LOW Voltage of RDY                           | Pull High Current = 1 mA                                |     |      | 0.5 | V    |

|                      |                                              |                                                         |     |      |     |      |

PFC OUTPUT DRIVER 1~3

| V <sub>GATE-CLAMP</sub> | Gate Output Clamping Voltage | V <sub>DD</sub> = 22 V                                                         | 13 | 15 | 17  | V  |

|-------------------------|------------------------------|--------------------------------------------------------------------------------|----|----|-----|----|

| V <sub>GATE-L</sub>     | Gate Low Voltage             | V <sub>DD</sub> = 15 V, I <sub>O</sub> = 100 mA                                |    |    | 1.5 | V  |

| $V_{GATE-H}$            | Gate High Voltage            | V <sub>DD</sub> = 13 V, I <sub>O</sub> = 100 mA                                | 8  |    |     | V  |

| t <sub>r</sub>          | Gate Rising Time             | $V_{DD}$ = 15 V, $C_L$ = 4.7 nF,<br>$V_{OPFC}$ from 2 V to 9 V                 |    | 70 |     | ns |

| t <sub>f</sub>          | Gate Falling Time            | $V_{DD}$ = 15 V, C <sub>L</sub> = 4.7 nF,<br>V <sub>OPFC</sub> from 9 V to 2 V |    | 60 |     | ns |

ΟΤΡ

|   | T <sub>OTP-ON</sub> | Over-Temperature Protection (Note 3) |  | 140 | °C   |

|---|---------------------|--------------------------------------|--|-----|------|

|   | $\Delta T_{OTP}$    | Hysteresis (Note 3)                  |  | 30  | °C   |

| _ |                     |                                      |  |     | <br> |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

This parameter, although guaranteed by design, is not 100% production tested.

The setting range of resistance at the RI pin is between 53.3 kΩ and 10.7 kΩ.

The setting range of resistance at the Ri pill

Frequency of AC input should be <75 Hz.</li>

The RLS and RGC setting suggestion follows the calculation result from application notes AN-4164 and AN-4165.

7. LPK specification is guaranteed at state of PFC working.

8. Pull the CM pin low to ground, ensuring VCM < 0.2 V, to enable an individual channel.

### THEORY OF OPERATION

#### **Continuous Conduction Mode (CCM)**

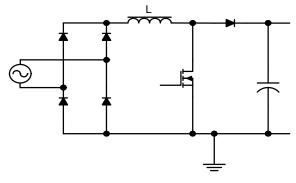

The boost converter, shown in Figure 4, is the most popular topology for power factor correction in AC–DC power supplies. This popularity can be attributed to the continuous input current waveform provided by the boost inductor and the boost converter's input voltage range low down to 0 V. These fundamental properties make close–to–unity power factor easier to achieve.

Figure 4. Basic PFC Boost Converter

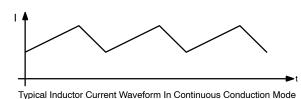

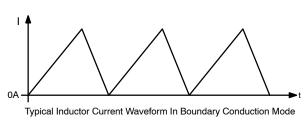

The boost converter can operate in Continuous Conduction Mode (CCM) or in Boundary Conduction Mode (BCM). These two descriptive names refer to the current flowing in the energy storage inductor of the boost power stage.

Figure 5. Basic PFC Boost Converter

As the names indicate, the inductor current in CCM is continuous and always above zero. In BCM, the new switching period is initiated when the inductor current returns to zero. There are many fundamental differences in CCM and BCM operations and the respective designs of the boost converter. The FAN9673 is design for CCM control, as Figure 5 shows. This method reduces inductor current ripple because the start current of each cycle is not 0 A typically. The ripple is controlled by the operation frequency and inductance design. This characteristic makes the peak current in the power semiconductor devices lower.

#### Gain Modulator (IA, LPK, VEA)

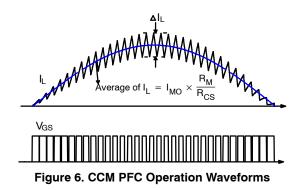

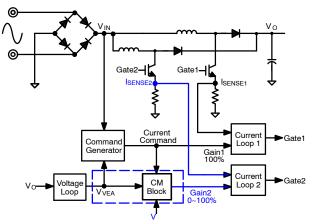

The FAN9673 employs two control loops for power factor correction: a current control loop and a voltage control loop. The current control loop shapes inductor current, as shown in Figure 6, through a current command, IMO, from the gain modulator.

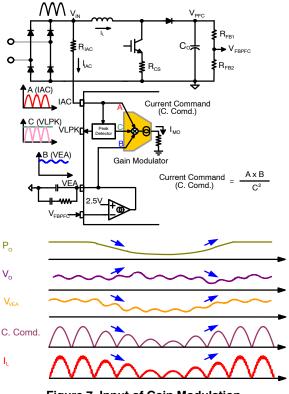

The gain modulator is the block that provides the reference to control PFC input current. The output signal of the gain modulator, IMO, is a function of VVEA, IIAC, and VLPK; as shown in the Figure 7.

These are the three inputs to the gain modulator:

- $I_{IAC}$ : A current representing the instantaneous input voltage (amplitude and wave shape) to the PFC. The rectified AC input sine wave is converted to a proportional current via a resistor and fed into the gain modulator. A sampling mechanism on  $I_{IAC}$  minimizes ground noise, important in high-power, switching-power conversion environment. The gain modulator responds linearly to  $I_{AC}$ .

- V<sub>LPK</sub>: Voltage proportional to the peak-voltage output of the bridge rectifier when the PFC is working. The signal is the output of peak-detect circuit detecting from the I<sub>AC</sub>. This factor of the gain modulator is input-voltage feed-forward control. This voltage information is not valid when the PFC is not working.

- V<sub>VEA</sub>: The output of the voltage error amplifier. The gain modulator responds linearly to variations of this voltage. The output of the gain modulator is a current signal, I<sub>MO</sub>,

as eq. 1:

$$I_{MO} = K \times \frac{I_{AC} \times V_{VEA}}{V_{LPK}^{2}}$$

(eq. 1)

where the K term is about 0.8 for  $V_{IR}$  < 1.5 V and 3.2 for  $V_{IR}$  > 3.5V respectively.

The current signal,  $I_{MO}$ , is in the form of a full–wave rectified sinusoid at twice of the line frequency. The gain modulator forms the reference for the current–loop and ultimately controls the instantaneous current drawn from the power line.

Figure 7. Input of Gain Modulation

#### **Current Balance**

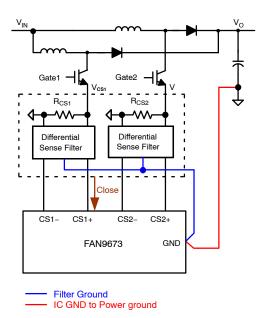

Current matching of different channel is an important topic of multi-channel control. In FAN9673, control of current in each channel is based on sensed signal  $V_{CS}$  to track the current command from the gain modulator, as shown in Figure 8.

Figure 8. Average Current Mode Control

The main factors to balance current in each channel are layout and device tolerance. The tolerance of the shunt resistor for the current sense is especially important. If the feedback signal,  $V_{CS}$ , has large deviation due to the tolerance of the sense resistor, the current of the channels tends to be unbalanced. High precision resistors are recommended.

High-power applications implies current values are high, so the distance of layout trace between the current sense resistors and the controller or power ground (negative of output capacitor) to IC ground is important, as shown in Figure 9. The longer trace and large current make the offset voltage and ground bounce differ significantly for different channels. Decreasing the deviation help balancing different channels. Please check the layout guidance in application notes AN-4164 or AN-4165.

**Figure 9. Current Balance Factors**

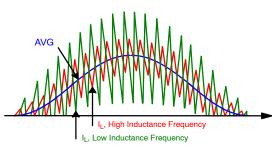

#### Interleaving

The FAN9673 controller is used to control three-channel boost converters connected in parallel. The controller operates in average-current mode and supports Continuous Conduction Mode (CCM). Each channel affords one-third the power when the system operates close to full load or when channel management is disabled.

Parallel power processing increases the number of power components, but the current rating of independent channels is reduced, allowing power semiconductors with lower current ratings to be applied.

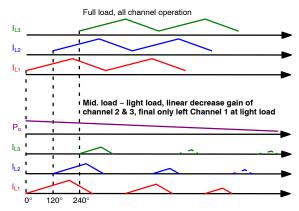

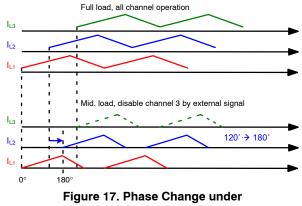

The switches of the three boost converters can operate at three–channel with 120° out–of–phase or two–channel with 180° out–of–phase (one channel disable at light load). The interleaving controller can reduce the total ripple current of input. Simultaneously, the output current ripple of each channel is evenly distributed and sequentially rippled on the output capacitor, which can extend the life of the capacitor.

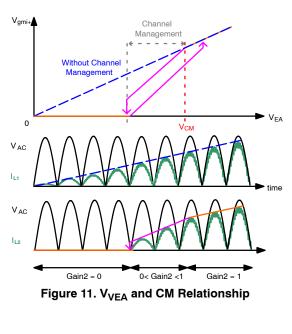

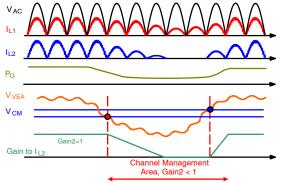

#### Channel Management 2/3: CM Control

The CM pin is used for controlling channel management. The channel management is realized by changing a gain, acting as changing relative weighting, for the current command. The relationship of CM and the gain of the slave channel is shown in Figure 10. The level of CM set the threshold of power level, representing by  $V_{VEA}$ , for reducing the current command for the slave PFC. The FAN9673 starts to reduce the current command ( $I_{MO} \times R_M$ ) for channel 2/3 by  $G_{ain2/3}$  from one to zero when the  $V_{VEA}$  level is lower than its CM level, as Figure 11 and Figure 12 show. The output power of the slave channel is reduced in response to reduction in current command. For example, when CM2 is set at 3 V and  $V_{VEA}$  is less than the CM2 voltage, the channel management block reduces the command for channel 2 as:

$$V_{gmi2+} = I_{MO} \times R_M \times G_{ain2}$$

(eq. 2)

Figure 10. Current Balance Factors

Figure 12.  $V_{VEA}$  and  $V_{CM}$  Relationship in Channel Management Operation

#### Table 2. PHASE AND GAIN CHANGE OF CM CONTROL

| CM (Channel Management)             | Phase and Gain |                      |                      |

|-------------------------------------|----------------|----------------------|----------------------|

|                                     | Channel 1      | Channel 2            | Channel 3            |

| Heavy Load (All Channel 100% Works) | 0° (Gain1 = 1) | 120° (Gain2 = 1)     | 240° (0 < Gain3 < 1) |

| Mid. Load (Channel 3 is Disabled)   | 0° (Gain1 = 1) | 120° (0 < Gain2 < 1) | Disable (Gain3 = 0)  |

| Light Load (Only Channel1 Left)     | 0° (Gain1 = 1) | Disable (Gain2 = 0)  | Disable (Gain3 = 0)  |

#### **Channel Management 2: External Control**

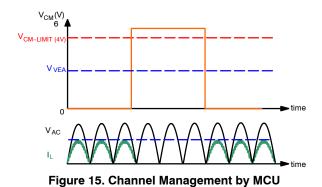

Channel Management (CM) function can also be accessed by an MCU through the connection shown in Figure 14. CM pins have internal pull–up current source. If  $V_{CM} > 4$  V, the channel is disabled. To enable the channel, make  $V_{CM} = 0$  V, as shown in Figure 15.

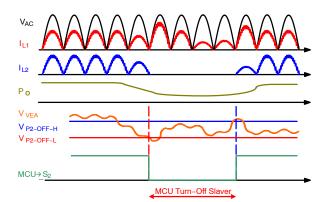

The CM pin of the slave should be connected with a switch  $S_2$  to ground. One pin of MCU must read the  $V_{VEA}$  signal to

Table 2 explains the phase and gain change of each channel when the PFC operates at various loads. The loading decreases the gain to the slave until it is disabled. The phase of Channel Management (CM) mode doesn't change when channel 3 is disabled. The behavior shown in Figure 13.

Figure 13. Phase and Gain Change of CM Control

determine when to turn on/off the slave channel. For example, as shown in Figure 16, two thresholds,  $V_{P2-OFF-L}$  and  $V_{P2-OFF-H}$ , are set in MCU program. When  $V_{VEA} < V_{P2-OFF-L}$ , the slave PFC turns off. If  $V_{VEA} > V_{P2-OFF-H}$ , the slave PFC turns on.

Figure 14. Channel Management by MCU

Figure 16. Channel Management by **External Signal from MCU**

| External Signal Control           | Phase<br>(Disable Channel: V <sub>CM</sub> > 4 V, Enable Channel: V <sub>CM</sub> = 0 V) |                                  |                                  |  |

|-----------------------------------|------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|--|

|                                   | Channel 1 Channel 2 Chann                                                                |                                  |                                  |  |

| Heavy Load (All Channels Enabled) | 0°                                                                                       | 120°                             | 240°                             |  |

| Mid. Load (Channel3 Disabled)     | 0°                                                                                       | 180°                             | Disable (V <sub>CM3</sub> > 4 V) |  |

| Light Load (Channel 2/3 Disabled) | 0°                                                                                       | Disable (V <sub>CM2</sub> > 4 V) | Disable (V <sub>CM3</sub> > 4 V) |  |

| Disable All System                | V <sub>CM1</sub> > 4 V, All Channels Disabled                                            |                                  |                                  |  |

When CM is accessed this way, relative phase of OPFC of each channel changes when the loading changes, as illustrated in Table 3 and Figure 17. When the MCU disables channel 3 at mid-load, the relative phase angle of channel 2 to channel 1 shifts from 120°C to 180°C.  $G_{ain2/3}$  of each channel under this control method switches between 100% and 0%.

**External Signal Control**

#### FUNCTIONAL DESCRIPTION

#### Internal Oscillator (RI)

Frequency of an internal oscillator is determined by an external resistor,  $R_{RI}$ , on the RI pin. The frequency of the oscillator is given by eq. 3. The frequency can be freely set in two ranges, 18 kHz ~ 40 kHz and 55 kHz~75 kHz. Setting frequency between 40 kHz and 55 kHz is not allowed in FAN9673.

$$f_{osc} = \frac{8 \times 10^8}{R_{RI}}$$

(eq. 3)

#### Current-Control Loop of Boost Stage

As shown in Figure 18, the two control loops for power factor correction are a current–control loop and a voltage–control loop. Based on the reference signal obtained at the IAC pin, the error amplifier in current–control loop regulates current signal as:

$$I_{L} \times R_{CS} = I_{MO} \times R_{M} \times G_{ain2/3} = K \times \frac{I_{AC} \times V_{EA}}{V_{LPK}^{2}} \times R_{M} \times G_{ain2/3}$$

(eq. 4)

Average value of sensed current,  $I_L \times R_{CS}$ , is regulated to the current command,  $I_{MO} \times R_M$ .  $G_{ain2/3}$  is a gain between  $0 \sim 1$  when the channel management block is engaged for the slave channels.  $G_{ain2/3}$  term is equal to one for channel 1.

#### Voltage–Control Loop of Boost Stage

The voltage–control loop regulates PFC output voltage by using the internal error amplifier,  $G_{mv}$ , making voltage on FBPFC same as the internal reference voltage, 2.5 V. It stabilizes PFC output voltage and decreases 120–Hz ripple on PFC output voltage.

Figure 18. Gain Modulation Block

#### **TriFault Detect Technology**

To improve power supply reliability, reduce system component count, and simplify compliance to UL 1950 safety standards, the FAN9673 brings TriFault Detect technology. This feature monitors FBPFC for certain PFC fault conditions.

In the case of a feedback path failure, the output of the PFC can exceed operating limits. Should FBPFC go too low, too high, or open, the TriFault Detect senses the fault and terminates the PFC output drive.

TriFault Detect is an entirely internal circuit. It requires no external components to perform its function.

#### PFC Over-Voltage Protection (OVP)

FAN9673 has an auto-restart OVP function. When the feedback level,  $V_{FBPFC}$ , reaches 2.75 V (reference level is 2.5 V), the PFC gate signal stops. The PFC gate signal resumes when  $V_{FBPFC}$  returns to 2.5 V.

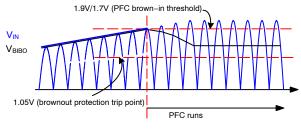

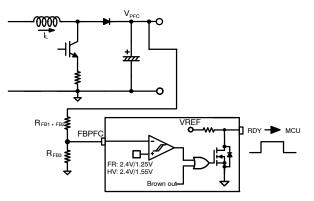

#### PFC Brown In/Out (BIBO)

An internal AC Under–Voltage Protection (UVP) comparator monitors the AC input information from  $V_{IN}$ , as shown in Figure 19. The OPFC is disabled when the  $V_{BIBO}$  is less than 1.05 V for 410 ms. If  $V_{BIBO}$  is larger than 1.9 V ( $V_{VIR} < 1.5$  V) or 1.75 V ( $V_{VIR} > 3.5$  V), the PFC stage is enabled. The VIR pin is used to set the AC input range according to Table 4.

#### Table 4. BIBO SETTING OF VARIOUS AC INPUT

| Input<br>Range | AC (V)    | R <sub>VIR</sub><br>Setting<br>(kΩ) | R <sub>IAC</sub><br>Setting<br>(MΩ) | BIBO Level (V) |

|----------------|-----------|-------------------------------------|-------------------------------------|----------------|

| Full-Range     | 85 ~ 264  | 10                                  | 6                                   | 85/75          |

| HV-Single      | 180 ~ 264 | 470                                 | 12                                  | 170/160        |

Figure 19.  $V_{\mbox{\scriptsize BIBO}}$  According to the PFC Operation

#### **PFC Gate Driver**

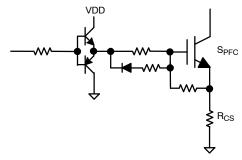

For high-power applications, the switch device of the system requires high driving current. The totem-pole circuit shown in Figure 20 is recommended.

Figure 20. Gate Drive Circuit

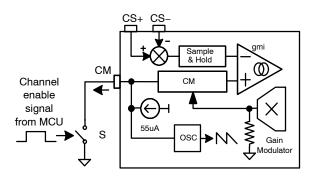

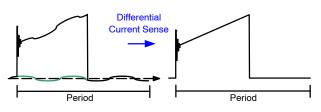

#### Differential Current Sensing (CS+, CS-)

Switching noise problems in interleaved PFC control is more critical than on a single channel, especially for current sensing. The FAN9673 uses a differential amplifier to eliminate switching noise from other channels. The FAN9673 has three groups of differential current-sensing pins. The CSn+ and CSn- are the inputs of the internal differential amplifiers. This makes the PFC more stable in higher-power applications and eliminates switching noise from other channels. As Figure 21 shows, ground bounce can be decreased by a differential sense function.

Figure 21. Gate Drive Circuit

#### Linear Predict Function (GC & LS)

Current sense signal reflects inductor current only when OPFC is on. The linear predict function is used to emulate the behavior of inductor current when the OPFC is off. Resistor on the LS pin is used to set equivalent inductance value for the internal emulator. Resistor on the GC pin is used to align sensed input voltage (IAC) and output voltage (FBPFC) signals. Values of those resistors can be determined by:

$$R_{LS} = \frac{L_{PFC}}{1.5 \times 10^{-9} \times R_{CS} \times \frac{(R_{FB1} + R_{FB2} + R_{FB3})}{R_{FB3}}}$$

(eq. 5)

$$R_{GC} = \frac{6 \times 10^{6}}{R_{B1} + R_{B2} + R_{B3}}$$

$$R_{GC} = \frac{1}{(\frac{R_{FB1} + R_{FB2} + R_{FB3}}{R_{FB3}})}$$

(eq. 6)

Care must be taken that RLS value need to be within 12~87 k $\Omega$ .

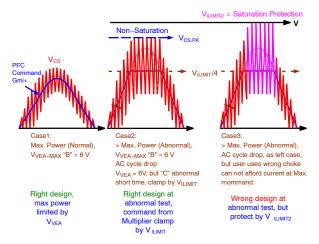

#### **Current–Limit Protection**

The FAN9673 includes three factors that limits current to manage OCP and inductor saturation:  $V_{VEA}$  limit,  $V_{ILIMIT}$ , and  $V_{ILIMIT2}$ . The current-limit thresholds,  $V_{ILIMIT1}$  and

$V_{ILIMIT2}$ , are configurable through ILIMIT and ILIMIT2 pins.

#### *Power (Normal State)*

In the normal case, average input power is controlled by the command  $V_{VEA}$ . When  $V_{VEA}$  rises to 5.6 V, it is internally clamped. Input power can't increase further.

#### Current Limit 1 (Abnormal State)

The current command from the gain modulator is  $K \times I_{AC} \times V_{VEA}/V_{LPK}^2$ . In abnormal state, such as AC cycle miss and recover in a short period, the  $V_{LPK}$  has a delay before returning to the original level. This delay makes the current command increased. If the command is greater than the limit clamp level,  $V_{ILIMIT}$ , current command will be clamped, as shown in Figure 22 and Figure 23. The peak current of this state can be used as the maximum current for inductor design, assuring inductor is not saturated.

Figure 22. Current Command Limit by ILIMIT

#### Current Limit 2 (Saturation State)

Use  $80\% \sim 90\%$  of the maximum current of the switch device to serve as the saturation protection. V<sub>LIMIT2</sub> is a cycle–by–cycle limit.

Figure 23. ILIMIT and ILIMIT2 Setting

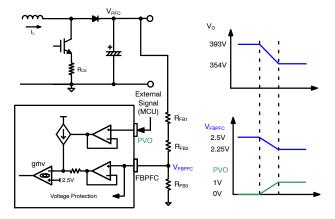

#### Programmable PFC Output Voltage (PVO)

In some cases, decreasing the PFC output voltage can improve efficiency of the PFC stage. The PVO pin is used to program output voltage, as shown in Figure 24. An external voltage signal, from MCU or other source, is provided to PVO pin.

This function is enabled when  $V_{PVO} > 0.5$  V. Upon enabled,  $V_{FBPFC}$  regulation target becomes:

$$V_{\text{FBPFC}} = 2.5 \text{ V} - \left[\frac{V_{\text{PVO}}}{4}\right] \quad (\text{eq. 7})$$

For instance, if PVO input is 1 V,  $R_{FB1}+R_{FB2} = 3.7 \text{ M}\Omega$ , and  $R_{FB3} = 23.7 \text{ k}\Omega$ ,  $V_{FBPFB}$  will be regulated to 2.25 V, making PFC  $V_O = 354 \text{ V}$ .

Figure 24. Programmable PFC Output Voltage

#### **RDY Function and AC Line Off/AC "SAG"**

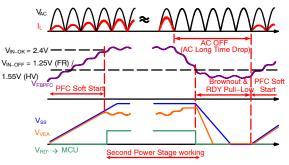

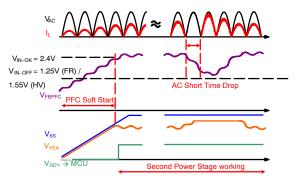

The ready (RDY) function is used to signal the MCU that the PFC stage is ready and the downstream power stage can start to operate. When the feedback voltage on FBPFC rises above 2.4 V,  $V_{RDY}$  signal pulls HIGH as shown in Figure 25.

If the AC line is OFF (or AC signal drops for a long time), the FAN9673 enters brown–out and  $V_{RDY}$  pulls LOW to indicate to the MCU that the power stage should stop, as shown in Figure 26.

When the AC signal drops for only a short time (i.e.  $1 \sim 1.5$  AC cycles), brown–out is not triggered and V<sub>FBPFC</sub> may not drop too much. In this case, RDY will not go LOW as shown in Figure 27.

AC "sag" means the AC drops to a low level, such as 110 V / 220 V  $\rightarrow$  40 V. AC "missing" means the AC drops to 0 V. If AC drops, the PFC attempts to transfer energy to V<sub>0</sub> before V<sub>0</sub> drops to the 50% level. If AC is 0 V, the PFC can't transfer energy. If the level reaches 50%, the PFC stops, and FAN9673 resets and waits for AC to return.

Figure 25. RDY Function to MCU

Figure 26. When AC Drops for a Long Time

Figure 27. AC Drops Briefly

#### Soft-Start

Soft-start is combined with RDY pin operation, as Figure 26 and Figure 27 show. During startup, the RDY pin remains LOW until the PFC output voltage reaches 96% of its nominal value. When the supply voltage of the downstream converter is controlled by the RDY pin, the PFC stage always starts with no load because the downstream converter does not operate until the PFC output voltage reaches the required level for the design.

Usually, the error amplifier output,  $V_{VEA}$ , is saturated to HIGH during startup because the actual output voltage is less than the target value.  $V_{VEA}$  remains saturated to HIGH until the PFC output voltage reaches its target value. Once the PFC output reaches its target value, the error amplifier comes out of saturation. However, it takes several line cycles for  $V_{VEA}$  to drop to its proper value for output regulation, which delivers more power to the load than required and causes output voltage overshoot. To prevent output voltage overshoot during startup caused by the saturation of error amplifier, the FAN9673 clamps the error amplifier output voltage ( $V_{EA}$ ) by the  $V_{SS}$  value until PFC output reaches 96% of its nominal value.

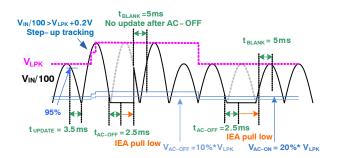

#### Input Voltage Peak Detection

The input AC peak voltage is sensed at the IAC pin. Ideally, RMS value of the input voltage should be used for feed-forward control in the gain modulator circuit. Since the RMS value of the AC input voltage is directly proportional to its peak, it is sufficient to find the peak instead of the more-complicated and slower method of integrating the input voltage over a half line cycle. The internal circuit of the IAC pin works with peak detection on the input AC waveform and output to the LPK pin for MCU use, as shown in Figure 28.

Figure 28. Waveform of LPK Function

One of the important benefits of this approach is that the peak indicates the correct RMS value even at no load. At no load, the HF filter capacitor at the input side of the boost converter is not discharged around the zero–crossing of the line waveform. Another notable benefit is that, during line transients, when the peak exceeds the previously measured value, the input–voltage feed–forward circuit can react immediately without waiting for a valid integral value at the end of the half–line period.

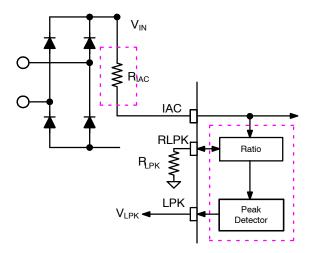

The relationship of  $V_{IN.PK}$  to  $V_{LPK}$  is shown in Figure 29. The peak detection circuits recognizes the  $V_{IN}$  information from  $I_{AC}$ . When recommended design values in Table 4 are followed, RLPK pin sets the ratio of  $V_{IN}$  to  $V_{LPK}$  via a resistor  $R_{RLPK}$  as described in eq. 8. The target value of  $V_{LPK}$  is usually set as one percent (1%) of  $V_{IN\_pk}$ . The maximum  $V_{LPK}$  should not exceed 3.8 V when system operation is at maximum AC input.

As in the below design example, assume the maximum  $V_{IN.PK}$  at 373 V (264  $V_{AC}$ ), the relationship of  $V_{IN.PK}/V_{LPK}$  is 100, and  $V_{LPK} = 3.73$  V < 3.8 V.