# LDO AND DUAL SWITCH WITH CONTROLLED RISE TIMES FOR DSP AND PORTABLE APPLICATIONS

## FEATURES

- Two 340-m $\Omega$  (Typical) High-Side MOSFETs

- 200 mA Low-Dropout Voltage Regulator In Fixed 3.3-V or Adjustable Versions

- Independent Thermal- and Short-Circuit Protection for LDO and Each Switch

- Overcurrent Indicators With Transient Filter

- 2.9-V to 5.5-V Operating Range

- CMOS- and TTL-Compatible Enable Inputs

- 75- $\mu$ A (Typical) Supply Current

- Available in 10-Pin MSOP or 14-Pin TSSOP (PowerPAD<sup>TM</sup>)

- $-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  Ambient Temperature Range

## APPLICATIONS

- USB Hubs and Peripherals

- Keyboards

- Zip Drives

- Speakers and Headsets

- PDAs and Portable Electronics

- DSP Power Sequencing

## DESCRIPTION

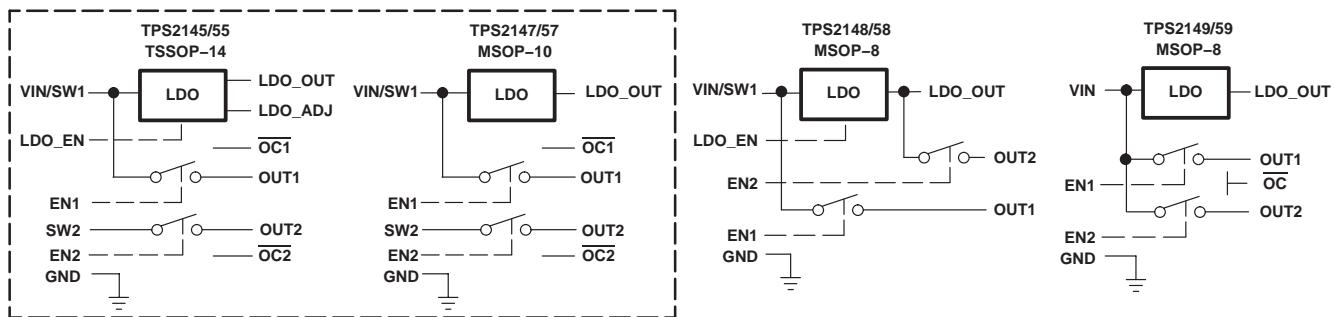

Two power-distribution switches and an adjustable (TPS2145) or fixed (TPS2147) LDO are incorporated in one small package, providing a power management solution that saves up to 60% in board space over typical implementations.

Designed to meet USB 2.0 bus-powered hub requirements, these devices also allow core and I/O voltage sequencing in DSP applications, or power segmentation in portable equipment. Each current-limited switch is a 340-m $\Omega$  N-channel MOSFET capable of supplying 200 mA of continuous current. A logic enable compatible with 5-V logic and 3-V logic controls each MOSFET as well as the LDO in the TPS2145. The internal charge pump provides the gate drive controlling the power-switch rise times and fall times, minimizing current surges during switching. The charge pump requires no external components.

The LDO has a drop-out voltage of only 0.35 V and with the independent enable on the TPS2145 LDO, the LDO can be used as an additional switch. The LDO output range for the TPS2145 is 1 V to 3.3 V, while the TPS2147 is fixed at 3.3 V.

The TPS2145 and TPS2147 have active-low switch enables and the TPS2155 and TPS2157 have active-high switch enables.

## LDO and dual switch family selection guide and schematics

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

**PRODUCTION DATA** information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

## AVAILABLE OPTIONS

| TA            | DESCRIPTION                                           | PACKAGE AND PIN COUNT | PACKAGED DEVICES    |                      |

|---------------|-------------------------------------------------------|-----------------------|---------------------|----------------------|

|               |                                                       |                       | ACTIVE LOW (SWITCH) | ACTIVE HIGH (SWITCH) |

| -40°C to 85°C | Adjustable LDO with LDO enable                        | TSSOP-14              | TPS2145IPWP         | TPS2155IPWP          |

|               | 3.3-V fixed LDO                                       | MSOP-10               | TPS2147IDGQ         | TPS2157IDGQ          |

|               | 3.3-V Fixed LDO with LDO enable and LDO output switch | MSOP-8                | TPS2148IDGN         | TPS2158IDGN          |

|               | 3.3-V Fixed LDO, shared input with switches           | MSOP-8                | TPS2149IDGN         | TPS2159IDGN          |

---

NOTE: All options available taped and reeled. Add an R suffix (e.g. TPS2145IPWPR)

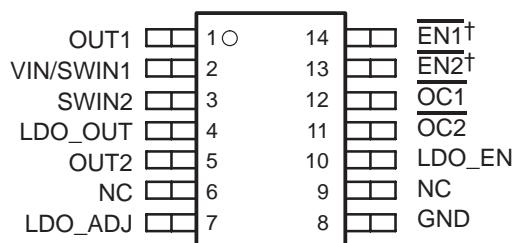

**TPS2145, TPS2155

TSSOP (PWP) PACKAGE

(TOP VIEW)**

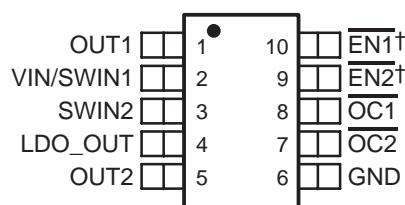

**TPS2147, TPS2157

MSOP (DGQ) PACKAGE

(TOP VIEW)**

<sup>†</sup> Pin 9 and 10 are active high for TPS2157.

NC – No internal connection

<sup>†</sup> Pin 13 and 14 are active high for TPS2155.

**absolute maximum ratings over operating free-air temperature (unless otherwise noted)†**

|                                                                                                      |                                      |

|------------------------------------------------------------------------------------------------------|--------------------------------------|

| Input voltage range: $V_{I(VIN/SWIN1)}$ , $V_{I(SWIN2)}$ , $V_{I(ENx)}$ , $V_{I(LDO\_EN)}$ . . . . . | –0.3 V to 6 V                        |

| Output voltage range: $V_{O(OUTx)}$ , $V_{O(LDO\_OUT)}$ , $V_{O(OCx)}$ . . . . .                     | –0.3 V to 6 V                        |

| Maximum output current, $I_{O(OCx)}$ . . . . .                                                       | ±10 mA                               |

| Continuous output current, $I_{O(OUTx)}$ , $I_{O(LDO\_OUT)}$ . . . . .                               | Internally limited                   |

| Continuous total power dissipation . . . . .                                                         | See Dissipation Rating Table         |

| Operating virtual-junction temperature range, $T_J$ . . . . .                                        | –40°C to 110°C                       |

| Storage temperature range, $T_{stg}$ . . . . .                                                       | –65°C to 150°C                       |

| Lead temperature soldering 1,6 mm (1/16 inch) from case for 10 seconds . . . . .                     | 260°C                                |

| Electrostatic discharge (ESD) protection: Human body model . . . . .                                 | 2 kV                                 |

|                                                                                                      | Charged device model (CDM) . . . . . |

|                                                                                                      | 1 kV                                 |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

† All voltages are with respect to GND.

## DISSIPATION RATING TABLE

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|---------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|

| MSOP10  | 1293.1 mW                             | 17.2 mW/°C                                     | 517.2 mW                              | 258.6 mW                              |

| PWP14   | 2000 mW                               | 26.6 mW/°C                                     | 800 mW                                | 400 mW                                |

**recommended operating conditions**

|                                                     |                  | MIN | MAX | UNIT |

|-----------------------------------------------------|------------------|-----|-----|------|

| Input voltage                                       | $V_I(VIN/SWIN1)$ | 2.9 | 5.5 | V    |

|                                                     | $V_I(SWIN2)$     | 2.9 | 5.5 |      |

|                                                     | $V_I(ENx)$       | 0   | 5.5 |      |

|                                                     | $V_I(LDO\_EN)$   | 0   | 5.5 |      |

| Continuous output current, $I_O$                    | LDO_OUT          |     | 200 | mA   |

|                                                     | OUT1, OUT2       |     | 150 |      |

| Output current limit, $I_O(LMT)$                    | LDO_OUT          | 275 | 550 | mA   |

|                                                     | OUT1, OUT2       | 200 | 400 |      |

| Operating virtual-junction temperature range, $T_J$ |                  | -40 | 100 | °C   |

**electrical characteristics over recommended operating junction-temperature range,

$2.9 \text{ V} \leq V_I(VIN/SWIN1) \leq 5.5 \text{ V}$ ,  $2.9 \text{ V} \leq V_I(SWIN2) \leq 5.5 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $100^\circ\text{C}$  (unless otherwise noted)**

**general**

| PARAMETER                                              | TEST CONDITIONS                                                                                                                                        | MIN                                                                          | TYP | MAX | UNIT |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----|-----|------|

| Off-state supply current                               | $V_I(ENx) = 5 \text{ V}$ (inactive),<br>$V_I(LDO\_EN) = 0 \text{ V}$ (inactive),<br>$V_O(LDO\_OUT) = \text{no load}$ ,<br>$V_O(OUTx) = \text{no load}$ |                                                                              | 20  |     | μA   |

| Forward leakage current                                | $V_I(VIN/SWIN1) = 5 \text{ V}$ ,<br>$V_I(SWIN2) = 5 \text{ V}$                                                                                         |                                                                              | 1   |     | μA   |

| $I_I$<br>Total input current at VIN/SWIN1<br>and SWIN2 | $V_I(VIN/SWIN1) = 5 \text{ V}$ ,<br>$V_I(SWIN2) = 5 \text{ V}$ ,<br>No load on OUTx,<br>No load on LDO_OUT                                             | $V_I(ENx) = \text{on}$ (active)                                              | 150 |     | μA   |

|                                                        |                                                                                                                                                        | $V_I(LDO\_EN) = 0 \text{ V}$ (inactive),<br>$V_I(ENx) = \text{on}$ (active)  | 100 |     | μA   |

|                                                        |                                                                                                                                                        | $V_I(LDO\_EN) = 5 \text{ V}$ (active),<br>$V_I(ENx) = \text{off}$ (inactive) | 100 |     | μA   |

**electrical characteristics over recommended operating junction-temperature range,

2.9 V  $\leq$   $V_I(VIN/SWIN1)$   $\leq$  5.5 V, 2.9 V  $\leq$   $V_I(SWIN2)$   $\leq$  5.5 V,  $V_I(ENx) = 0$  V or  $V_I(ENx) = 5$  V,

$V_I(LDO\_EN) = 5$  V,  $T_J = -40^\circ\text{C}$  to  $100^\circ\text{C}$  (unless otherwise noted)**

**power switches**

| PARAMETER                                       |                                                                        | TEST CONDITIONS                                                                                                       | MIN                                                                                      | TYP | MAX | UNIT             |

|-------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----|-----|------------------|

| $r_{DS(on)}$                                    | Static drain-source on-state resistance,<br>VIN/SWIN1 or SWIN2 to OUTx | $T_J = -40^\circ\text{C}$ to $100^\circ\text{C}$ ,<br>$I_O(LDO\_OUT) = 200$ mA,<br>$I_{OUT1}$ and $I_{OUT2} = 150$ mA |                                                                                          | 580 | 340 | $\text{m}\Omega$ |

|                                                 |                                                                        | $T_J = 25^\circ\text{C}$ ,<br>$I_O(LDO\_OUT) = 200$ mA,<br>$I_{OUT1}$ and $I_{OUT2} = 150$ mA                         |                                                                                          |     |     |                  |

| $I_{lkg(R)}$                                    | Reverse leakage current at OUTx                                        | $V_O(OUTx) = 5$ V,<br>$LDO\_EN$ = don't care                                                                          | $V_I(ENx) = 5$ V,<br>$V_I(ENx) = 0$ V,<br>$SWIN2$ floating,<br>$V_I(VIN/SWIN1) = 5$ V    | 10  | 10  | $\mu\text{A}$    |

|                                                 |                                                                        |                                                                                                                       | $V_I(ENx) = 5$ V,<br>$V_I(ENx) = 0$ V,<br>$V_I(SWIN2) = 0$ ,<br>$V_I(VIN/SWIN1) = 2.9$ V |     |     |                  |

|                                                 |                                                                        |                                                                                                                       | $V_I(ENx) = 5$ V,<br>$V_I(ENx) = 0$ V,<br>$V_I(SWIN2) = 0$ ,<br>$V_I(VIN/SWIN1) = 0$ V   |     |     |                  |

| $I_{OS}$                                        | Short circuit output current                                           | OUTx connected to GND, device enabled into short circuit                                                              | 0.2                                                                                      | 0.4 | 0.4 | A                |

| Delay time for asserting $\overline{OC}$ flag   |                                                                        | From $I_{OUTx}$ at 95% of current limit level to 50% $\overline{OC}$                                                  | 5.5                                                                                      |     | ms  |                  |

| Delay time for deasserting $\overline{OC}$ flag |                                                                        | From $I_{OUTx}$ at 95% of current limit level to 50% $\overline{OC}$                                                  | 10.5                                                                                     |     | ms  |                  |

**timing parameters, power switches**

| PARAMETER |                                        | TEST CONDITIONS         | MIN               | TYP  | MAX | UNIT |

|-----------|----------------------------------------|-------------------------|-------------------|------|-----|------|

| $t_{on}$  | Turnon time, OUTx switch, (see Note 1) | $C_L = 100 \mu\text{F}$ | $R_L = 33 \Omega$ | 0.5  | 6   | ms   |

|           |                                        | $C_L = 1 \mu\text{F}$   |                   | 0.1  | 3   |      |

| $t_{off}$ | Turnoff time, OUTx switch (see Note 1) | $C_L = 100 \mu\text{F}$ | $R_L = 33 \Omega$ | 5.5  | 12  |      |

|           |                                        | $C_L = 1 \mu\text{F}$   |                   | 0.05 | 4   |      |

| $t_r$     | Rise time, OUTx switch (see Note 1)    | $C_L = 100 \mu\text{F}$ | $R_L = 33 \Omega$ | 0.5  | 5   |      |

|           |                                        | $C_L = 1 \mu\text{F}$   |                   | 0.1  | 2   |      |

| $t_f$     | Fall time, OUTx switch (see Note 1)    | $C_L = 100 \mu\text{F}$ | $R_L = 33 \Omega$ | 5.5  | 9   |      |

|           |                                        | $C_L = 1 \mu\text{F}$   |                   | 0.05 | 1.2 |      |

NOTE 1. Specified by design, not tested in production.

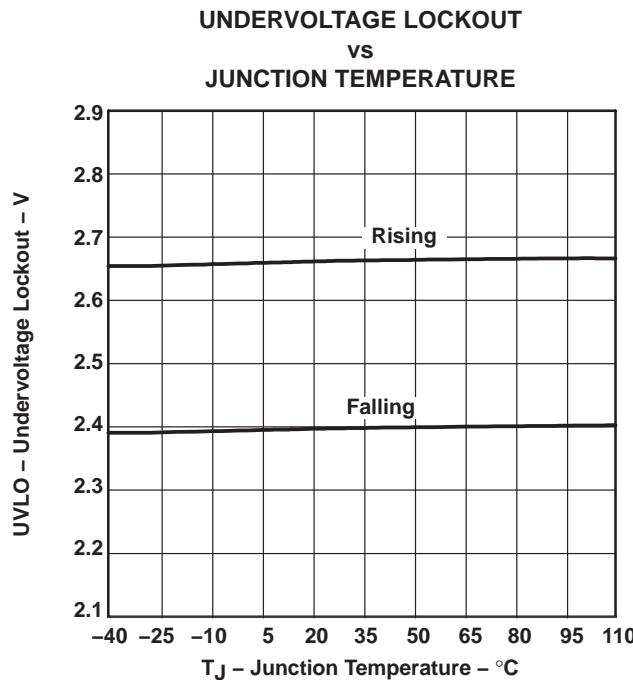

**undervoltage lockout at VIN/SWIN1**

| PARAMETER               | TEST CONDITIONS | MIN | TYP  | MAX           | UNIT |

|-------------------------|-----------------|-----|------|---------------|------|

| UVLO Threshold          |                 | 2.2 | 2.85 |               | V    |

| Hysteresis (see Note 1) |                 | 260 |      | mV            |      |

| Deglitch (see Note 1)   |                 | 50  |      | $\mu\text{s}$ |      |

NOTE 1. Specified by design, not tested in production.

**electrical characteristics over recommended operating junction-temperature range,

$2.9 \text{ V} \leq V_I(\text{VIN}/\text{SWIN1}) \leq 5.5 \text{ V}$ ,  $2.9 \text{ V} \leq V_I(\text{SWIN2}) \leq 5.5 \text{ V}$ ,  $V_I(\text{ENx}) = 0 \text{ V}$  or  $V_I(\text{ENx}) = 5 \text{ V}$ ,

$V_I(\text{LDO\_EN}) = 5 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $100^\circ\text{C}$  (unless otherwise noted) (continued)**

#### undervoltage lockout at SWIN2

| PARAMETER               | TEST CONDITIONS | MIN | TYP  | MAX | UNIT |

|-------------------------|-----------------|-----|------|-----|------|

| UVLO Threshold          |                 | 2.2 | 2.85 |     | V    |

| Hysteresis (see Note 1) |                 | 260 |      |     | mV   |

| Deglitch (see Note 1)   |                 | 50  |      |     | μs   |

NOTE 1. Specified by design, not tested in production.

**electrical characteristics over recommended operating junction-temperature range,

$2.9 \text{ V} \leq V_I(\text{VIN}/\text{SWIN1}) \leq 5.5 \text{ V}$ ,  $2.9 \text{ V} \leq V_I(\text{SWIN2}) \leq 5.5 \text{ V}$ ,  $V_I(\text{ENx}) = 0 \text{ V}$  or  $V_I(\text{ENx}) = 5 \text{ V}$ ,

$V_I(\text{LDO\_EN}) = 5 \text{ V}$ ,  $C_L(\text{LDO\_OUT}) = 10 \text{ μF}$ ,  $T_J = -40^\circ\text{C}$  to  $100^\circ\text{C}$  (unless otherwise noted)**

#### fixed-voltage regulator, 3.3 V

| PARAMETER                            | TEST CONDITIONS <sup>†</sup>                                                                                                                                                                                 | MIN   | TYP  | MAX   | UNIT |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| $V_O$                                | $V_I(\text{VIN}/\text{SWIN1}) = 4.25 \text{ V}$ to $5.25 \text{ V}$ ,<br>$I_O(\text{LDO\_OUT}) = 0.5 \text{ mA}$ to $200 \text{ mA}$                                                                         | 3.20  | 3.3  | 3.40  | V    |

| Dropout voltage                      | $V_I(\text{VIN}/\text{SWIN1}) = 3.2 \text{ V}$ ,<br>$I_O(\text{LDO\_OUT}) = 200 \text{ mA}$ ,<br>$I_O(\text{OUT1}) = 150 \text{ mA}$                                                                         |       |      | 0.35  | V    |

| Line regulation voltage (see Note 1) | $V_I(\text{VIN}/\text{SWIN1}) = 4.25 \text{ V}$ to $5.25 \text{ V}$ ,<br>$I_O(\text{LDO\_OUT}) = 5 \text{ mA}$                                                                                               |       |      | 0.1   | %/V  |

| Load regulation voltage (see Note 1) | $V_I(\text{VIN}/\text{SWIN1}) = 4.25 \text{ V}$ ,<br>$I_O(\text{LDO\_OUT}) = 5 \text{ mA}$ to $200 \text{ mA}$                                                                                               |       | 0.4% | 1.15% |      |

| $I_{OS}$                             | $V_I(\text{VIN}/\text{SWIN1}) = 4.25 \text{ V}$ ,<br>$\text{LDO\_OUT}$ connected to GND                                                                                                                      | 0.275 | 0.33 | 0.55  | A    |

| $I_{lkg(R)}$                         | $V_O(\text{LDO\_OUT}) = 3.3 \text{ V}$ ,<br>$V_I(\text{VIN}/\text{SWIN1}) = 0 \text{ V}$ ,<br>$V_I(\text{LDO\_EN}) = 0 \text{ V}$                                                                            |       | 10   |       | μA   |

|                                      | $V_O(\text{LDO\_OUT}) = 5.5 \text{ V}$ ,<br>$V_I(\text{VIN}/\text{SWIN1}) = 2.9 \text{ V}$ ,<br>$V_I(\text{LDO\_EN}) = 0 \text{ V}$                                                                          |       | 10   |       | μA   |

| $t_{on}$                             | Turnoff time, LDO_EN transitioning low (see Note 1)<br>$R_L = 16 \text{ Ω}$ , $C_L(\text{LDO\_OUT}) = 10 \text{ μF}$                                                                                         | 0.25  | 1    |       | ms   |

| $t_{off}$                            | Turnon time, LDO_EN transitioning high (see Note 1)<br>$R_L = 16 \text{ Ω}$ , $C_L(\text{LDO\_OUT}) = 10 \text{ μF}$                                                                                         | 0.1   | 1    |       | ms   |

|                                      | Ramp-up time, LDO_OUT (0% to 90%)<br>$V_I(\text{LDO\_EN}) = 5 \text{ V}$ , VIN/SWIN1 ramping up from 10% to 90% in 0.1 ms, $R_L = 16 \text{ Ω}$ , $C_L(\text{LDO\_OUT}) = 10 \text{ μF}$                     | 0.1   | 1    |       | ms   |

|                                      | Power supply rejection<br>$f = 1 \text{ kHz}$ , $C_L(\text{LDO\_OUT}) = 4.7 \text{ μF}$ ,<br>$\text{ESR} = 0.25 \text{ Ω}$ , $I_O = 5 \text{ mA}$ ,<br>$V_I(\text{VIN}/\text{SWIN1})_{p-p} = 100 \text{ mV}$ |       | 50   |       | dB   |

<sup>†</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

NOTE 1. Specified by design, not tested in production.

**electrical characteristics over recommended operating junction-temperature range,

$2.9 \text{ V} \leq V_I(\text{VIN}/\text{SWIN1}) \leq 5.5 \text{ V}$ ,  $2.9 \text{ V} \leq V_I(\text{SWIN2}) \leq 5.5 \text{ V}$ ,  $V_I(\text{ENx}) = 0 \text{ V}$  or  $V_I(\text{ENx}) = 5 \text{ V}$ ,

$V_I(\text{LDO\_EN}) = 5 \text{ V}$ ,  $C_L(\text{LDO\_OUT}) = 10 \mu\text{F}$ ,  $T_J = -40^\circ\text{C}$  to  $100^\circ\text{C}$  (unless otherwise noted) (continued)**

**adjustable voltage regulator ( $V_x = 1 \text{ V}$  to  $3.3 \text{ V}$ )**

| PARAMETER                                                                                                                                                                                                       |                                                               | TEST CONDITIONS <sup>†</sup>                                                                                                                                                                    | MIN        | TYP   | MAX        | UNIT          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|------------|---------------|

| $V_O$                                                                                                                                                                                                           | Output voltage, dc (see Note 2)                               | $V_I(\text{VIN}/\text{SWIN1}) = V_x + 0.6 \text{ V}$ to $5.5 \text{ V}$ and<br>$V_I(\text{VIN}/\text{SWIN1}) > 2.9 \text{ V}$ ,<br>$I_O = 0.5 \text{ mA}$ to $200 \text{ mA}$                   | 0.97 $V_x$ | $V_x$ | 1.03 $V_x$ | V             |

| Dropout voltage ( $\text{VIN}/\text{SWIN1}$ to $\text{LDO\_OUT}$ )                                                                                                                                              |                                                               | $V_I(\text{VIN}/\text{SWIN1}) = V_x - 0.1 \text{ V}$ , $I_O = 200 \text{ mA}$                                                                                                                   |            | 0.5   |            | V             |

| Line regulation voltage (see Note 1)                                                                                                                                                                            |                                                               | $V_I(\text{VIN}/\text{SWIN1}) = V_x + 0.6 \text{ V}$ to $5.5 \text{ V}$ and<br>$V_I(\text{VIN}/\text{SWIN1}) > 2.9 \text{ V}$ ,<br>$I_O = 5 \text{ mA}$                                         |            | 0.1   |            | %/V           |

| Load regulation voltage (see Note 1)                                                                                                                                                                            |                                                               | $V_I(\text{VIN}/\text{SWIN1}) = V_x + 0.6 \text{ V}$ to $5.5 \text{ V}$ and<br>$V_I(\text{VIN}/\text{SWIN1}) > 2.9 \text{ V}$ ,<br>$I_O = 5 \text{ mA}$ to $200 \text{ mA}$                     |            | 0.4%  | 1%         |               |

| $I_{OS}$                                                                                                                                                                                                        | Short-circuit current limit                                   | $V_I(\text{VIN}/\text{SWIN1}) = V_x + 0.6 \text{ V}$ to $5.5 \text{ V}$ and<br>$V_I(\text{VIN}/\text{SWIN1}) > 2.9 \text{ V}$ ,<br>$\text{LDO\_OUT}$ connected to GND                           | 0.275      | 0.33  | 0.575      | A             |

| $I_{lkg(R)}$                                                                                                                                                                                                    | Reverse leakage current into $\text{LDO\_OUT}$                | $V_O(\text{LDO\_OUT}) = V_x$ ,<br>$V_I(\text{VIN}/\text{SWIN1}) = 0 \text{ V}$ ,<br>$V_I(\text{LDO\_EN}) = 0 \text{ V}$                                                                         |            | 10    |            | $\mu\text{A}$ |

|                                                                                                                                                                                                                 |                                                               | $V_O(\text{LDO\_OUT}) = 5.5 \text{ V}$ ,<br>$V_I(\text{VIN}/\text{SWIN1}) = 2.8 \text{ V}$ ,<br>$V_I(\text{LDO\_EN}) = 0 \text{ V}$                                                             |            | 10    |            | $\mu\text{A}$ |

| $t_{on}$                                                                                                                                                                                                        | Turnoff time, $\text{LDO\_EN}$ transitioning low (see Note 1) | From 50% $\text{LDO\_EN}$ to 10% $\text{LDO\_OUT}$ ,<br>$R_L = V_x/0.2 \Omega$ , $C_L(\text{LDO\_OUT}) = 10 \mu\text{F}$                                                                        | 0.1        | 1     |            | ms            |

| $t_{off}$                                                                                                                                                                                                       | Turnon time, $\text{LDO\_EN}$ transitioning high (see Note 1) | From 50% $\text{LDO\_EN}$ to 90% $\text{LDO\_OUT}$ ,<br>$R_L = V_x/0.2 \Omega$ , $C_L(\text{LDO\_OUT}) = 10 \mu\text{F}$                                                                        | 0.1        | 1     |            | ms            |

| Ramp-up time, $\text{LDO\_OUT}$ (0% to 90%)                                                                                                                                                                     |                                                               | $V_I(\text{LDO\_EN}) = 5 \text{ V}$ , $\text{VIN}/\text{SWIN1}$ ramping up from 10% to 90% in 0.1 ms, $R_L = V_x/0.2 \Omega$ ,<br>$C_L(\text{LDO\_OUT}) = 10 \mu\text{F}$                       | 0.1        | 1     |            | ms            |

| Output tracking<br>$\text{OUT1}$ lag time from $\text{LDO\_OUT}$ given<br>$\text{LDO\_EN}$ and $\text{EN1}$ have been asserted simultaneously to turnon their respective outputs. Measured at 1 V. (see Note 1) |                                                               | $\text{LDO load } R_L = V_x/0.2 \Omega$ ,<br>$C_L(\text{LDO\_OUT}) = 10 \mu\text{F}$ ,<br>$\text{OUT1 } R_L = 33 \Omega$ , $10 \mu\text{F}$ ,<br>$V_I(\text{VIN}/\text{SWIN1}) = 3.3 \text{ V}$ | 0          | 1     |            | ms            |

| Power supply rejection                                                                                                                                                                                          |                                                               | $f = 1 \text{ kHz}$ , $C_L(\text{LDO\_OUT}) = 4.7 \mu\text{F}$ ,<br>$\text{ESR} = 0.25 \Omega$ , $I_O = 5 \text{ mA}$ ,<br>$V_I(\text{VIN}/\text{SWIN1})_{\text{p-p}} = 100 \text{ mV}$         |            | 50    |            | dB            |

<sup>†</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

NOTES: 1. Specified by design, not tested in production.

2. Does not include error introduced by external resistive divider  $R_1$ ,  $R_2$  tolerance.

**electrical characteristics over recommended operating junction-temperature range,

$2.9 \text{ V} \leq V_I(\text{VIN}/\text{SWIN1}) \leq 5.5 \text{ V}$ ,  $2.9 \text{ V} \leq V_I(\text{SWIN2}) \leq 5.5 \text{ V}$ ,  $V_I(\text{ENx}) = 0 \text{ V}$  or  $V_I(\text{ENx}) = 5 \text{ V}$ ,

$V_I(\text{LDO\_EN}) = 5 \text{ V}$ ,  $T_J = -40^\circ\text{C}$  to  $100^\circ\text{C}$  (unless otherwise noted)**

**enable input,  $\overline{\text{ENx}}$  (active low)**

| PARAMETER                               | TEST CONDITIONS                 | MIN | TYP | MAX | UNIT          |

|-----------------------------------------|---------------------------------|-----|-----|-----|---------------|

| $V_{IH}$<br>High-level input voltage    |                                 | 2   |     |     | V             |

| $V_{IL}$<br>Low-level input voltage     |                                 |     | 0.8 |     | V             |

| $I_I$<br>Input current, pullup (source) | $V_I(\text{ENx}) = 0 \text{ V}$ |     | 5   |     | $\mu\text{A}$ |

**enable input,  $\text{ENx}$  (active high)**

| PARAMETER                               | TEST CONDITIONS                 | MIN | TYP | MAX | UNIT          |

|-----------------------------------------|---------------------------------|-----|-----|-----|---------------|

| $V_{IH}$<br>High-level input voltage    |                                 | 2   |     |     | V             |

| $V_{IL}$<br>Low-level input voltage     |                                 |     | 0.8 |     | V             |

| $I_I$<br>Input current, pulldown (sink) | $V_I(\text{ENx}) = 5 \text{ V}$ |     | 5   |     | $\mu\text{A}$ |

**enable input,  $\text{LDO\_EN}$  (active high)**

| PARAMETER                            | TEST CONDITIONS                     | MIN | TYP | MAX | UNIT          |

|--------------------------------------|-------------------------------------|-----|-----|-----|---------------|

| $V_{IH}$<br>High-level input voltage |                                     | 2   |     |     | V             |

| $V_{IL}$<br>Low-level input voltage  |                                     |     | 0.8 |     | V             |

| $I_I$<br>Input current, pulldown     | $V_I(\text{LDO\_EN}) = 5 \text{ V}$ |     | 5   |     | $\mu\text{A}$ |

| Falling-edge deglitch (see Note 1)   |                                     | 50  |     |     | $\mu\text{s}$ |

NOTE 1. Specified by design, not tested in production.

**logic output,  $\overline{\text{OCx}}$**

| PARAMETER                                | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------------------------|-----------------|-----|-----|-----|------|

| Current sinking at $V_O = 0.4 \text{ V}$ |                 | 1   |     |     | mA   |

**thermal shutdown characteristics**

| PARAMETER                                                              | TEST CONDITIONS                                                       | MIN | TYP | MAX | UNIT             |

|------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|------------------|

| First thermal shutdown (shuts down switch or regulator in overcurrent) | Occurs at or above specified temperature when overcurrent is present. | 120 |     |     | $^\circ\text{C}$ |

| Recovery from thermal shutdown                                         |                                                                       | 110 |     |     |                  |

| Second thermal shutdown (shuts down all switches and regulator)        | Occurs on rising temperature, irrespective of overcurrent.            | 155 |     |     |                  |

| Second thermal shutdown hysteresis                                     |                                                                       | 10  |     |     |                  |

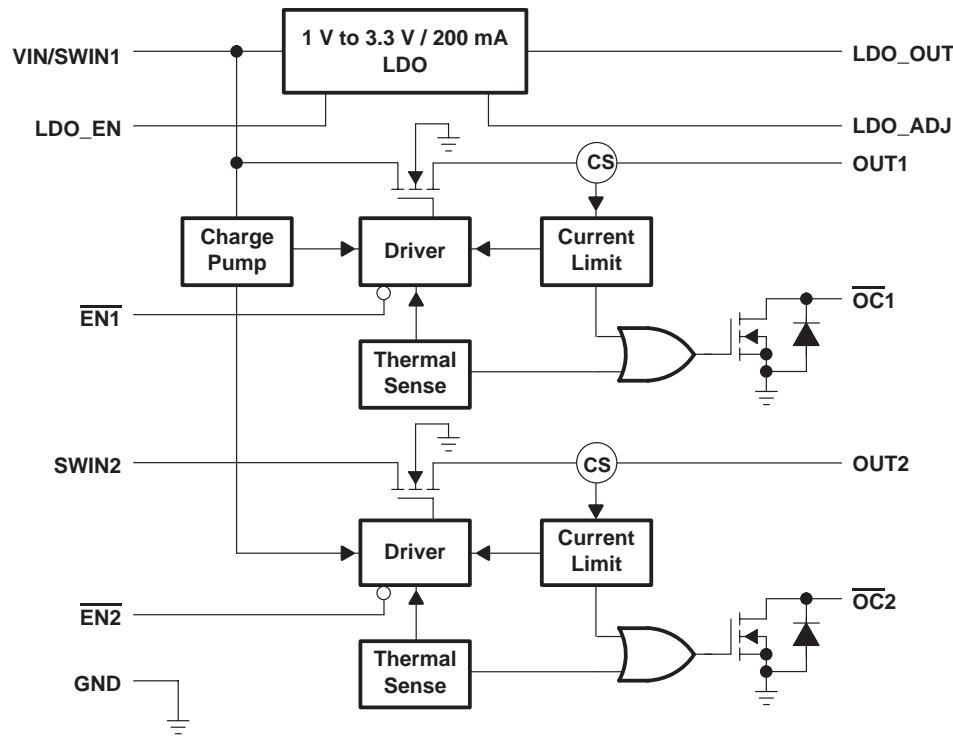

**TPS2145 functional block diagram**

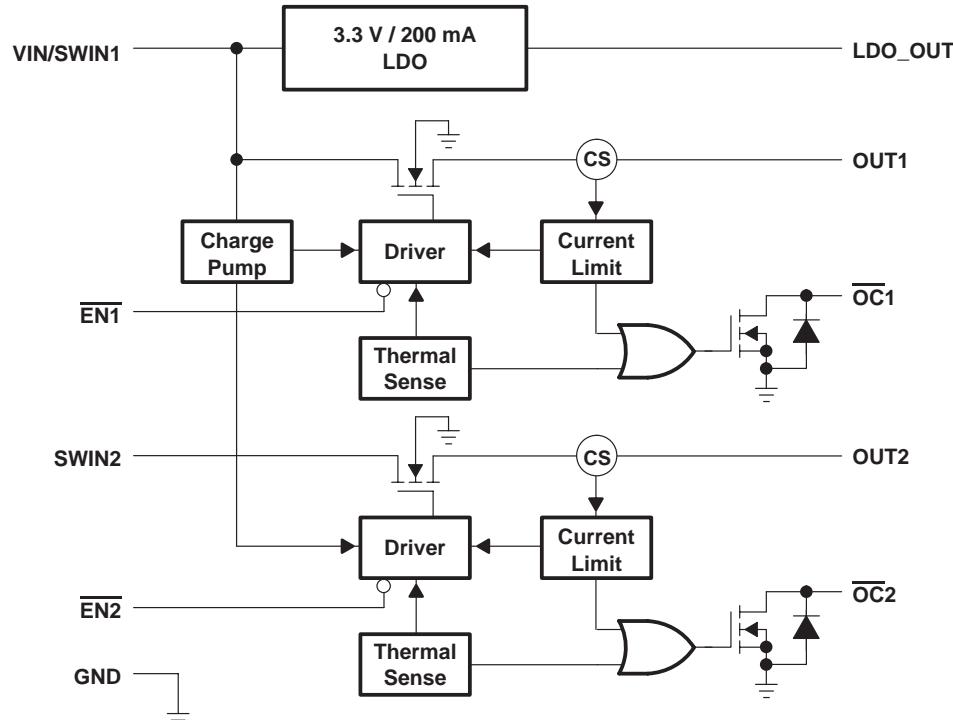

**TPS2147 functional block diagram**

## Terminal Functions

| NAME      | TERMINAL |         |         |         | I/O | DESCRIPTION                                          |  |  |

|-----------|----------|---------|---------|---------|-----|------------------------------------------------------|--|--|

|           | NO.      |         |         |         |     |                                                      |  |  |

|           | PWP-14   |         | DGQ-10  |         |     |                                                      |  |  |

|           | TPS2145  | TPS2155 | TPS2147 | TPS2157 |     |                                                      |  |  |

| EN1       |          | 14      |         | 10      | I   | Logic level enable to transfer power to OUT1         |  |  |

| EN1       | 14       |         | 10      |         |     |                                                      |  |  |

| EN2       |          | 13      |         | 9       | I   | Logic level enable to transfer power to OUT2         |  |  |

| EN2       | 13       |         | 9       |         |     |                                                      |  |  |

| GND       | 8        | 8       | 6       | 6       |     | Ground                                               |  |  |

| LDO_ADJ   | 7        | 7       |         |         | I   | User feedback for adjustable regulator               |  |  |

| LDO_EN    | 10       | 10      |         |         | I   | Logic level LDO enable. Active high.                 |  |  |

| LDO_OUT   | 4        | 4       | 4       | 4       | O   | LDO output                                           |  |  |

| NC        | 6, 9     | 6, 9    |         |         |     | No connection                                        |  |  |

| OC1       | 12       | 12      | 8       | 8       | O   | Overcurrent status flag for OUT1. Open-drain output. |  |  |

| OC2       | 11       | 11      | 7       | 7       | O   | Overcurrent status flag for OUT2. Open-drain output. |  |  |

| OUT1      | 1        | 1       | 1       | 1       | O   | Switch 1 output                                      |  |  |

| OUT2      | 5        | 5       | 5       | 5       |     | Switch 2 output                                      |  |  |

| SWIN2     | 3        | 3       | 3       | 3       | I   | Input for switch 2                                   |  |  |

| VIN/SWIN1 | 2        | 2       | 2       | 2       | I   | Input for LDO and switch 1; device supply voltage    |  |  |

### detailed description

#### VIN/SWIN1

The VIN/SWIN1 serves as the input to the internal LDO and as the input to one N-channel MOSFET. The fixed or adjustable LDO has a dropout voltage of 0.35 V and is rated for 200 mA of continuous current. The power switch is an N-channel MOSFET with a maximum on-state resistance of 580 mΩ. Configured as a high-side switch, the power switch prevents current flow from OUT to IN and IN to OUT when disabled. The power switch is rated at 200 mA, continuous current. VIN/SWIN1 must be connected to a voltage source for device operation.

#### SWIN2

SWIN2 is the input to the other N-channel MOSFET, which also has a maximum on-state resistance of 580 mΩ. Configured as a high-side switch, the power switch prevents current flow from OUT to IN and IN to OUT when disabled. The power switch is rated at 200 mA, continuous current.

#### OUTx

OUT1 and OUT2 are the outputs from the internal power-distribution switches.

#### LDO\_OUT

LDO\_OUT is the output of the internal 200-mA LDO. The fixed version of the LDO has an output of 3.3 V. The adjustable version has an output voltage range of 1 V to 3.3 V.

#### LDO\_ADJ

This input only applies to the adjustable LDO version of this device (TPS2145/55). LDO\_ADJ is used to adjust the output voltage anywhere between 1 V and 3.3 V.

#### LDO\_EN

The active high input, LDO\_EN, only applies to the adjustable LDO version of this device (TPS2145/55). LDO\_EN is used to enable the internal LDO and is compatible with TTL and CMOS logic.

## **detailed description (continued)**

### **enable ( $\overline{EN_x}$ , $EN_x$ )**

The logic enable disables the power switch. Both switches have independent enables and are compatible with both TTL and CMOS logic.

### **overcurrent ( $\overline{OC_x}$ )**

The  $\overline{OC_x}$  open-drain output is asserted (active low) when an overcurrent condition is encountered. The output will remain asserted until the overcurrent condition is removed.

### **current sense**

A sense FET monitors the current supplied to the load. Current is measured more efficiently by the sense FET than by conventional resistance methods. When an overload or short circuit is encountered, the current-sense circuitry sends a control signal to the driver. The driver in turn reduces the gate voltage and drives the power FET into its saturation region, which switches the output into a constant-current mode and holds the current constant while varying the voltage on the load.

### **thermal sense**

A dual-threshold thermal trip is implemented to allow fully independent operation of the power distribution switches. In an overcurrent or short-circuit condition, the junction temperature rises. When the die temperature rises to approximately 120°C, the internal thermal sense circuitry determines which power switch is in an overcurrent condition and turns off that switch, thus isolating the fault without interrupting operation of the adjacent power switch. Because hysteresis is built into the thermal sense, the switch turns back on after the device has cooled approximately 10 degrees. The switch continues to cycle off and on until the fault is removed.

### **undervoltage lockout**

A voltage sense circuit monitors the input voltage. When the input voltage is below approximately 2.5 V, a control signal turns off the power switch.

---

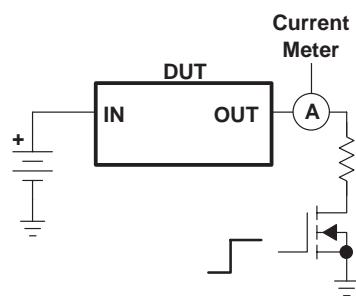

## **PARAMETER MEASUREMENT INFORMATION**

**Figure 1. Current Limit Test Circuit**

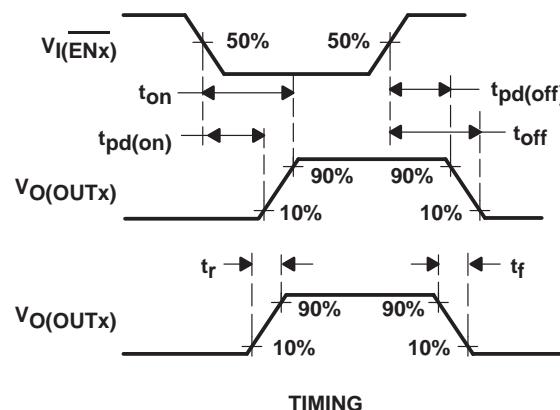

## PARAMETER MEASUREMENT INFORMATION

Figure 2. Timing and Internal Voltage Regulator Transition Waveforms

## TYPICAL CHARACTERISTICS

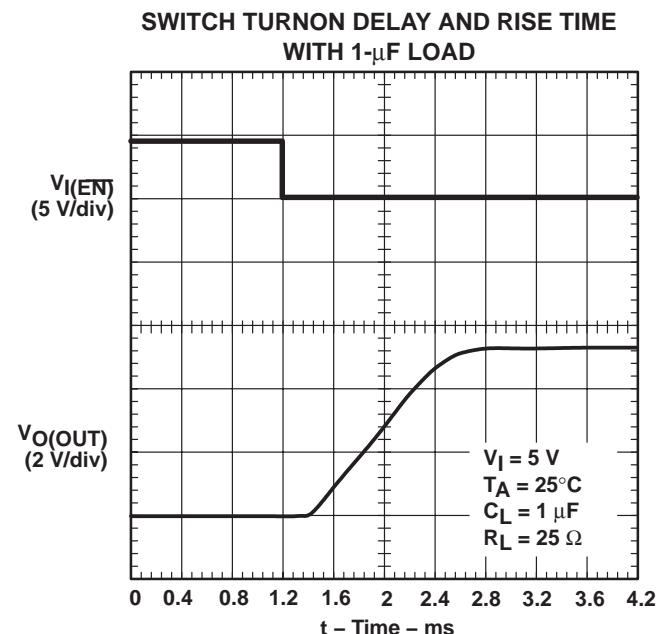

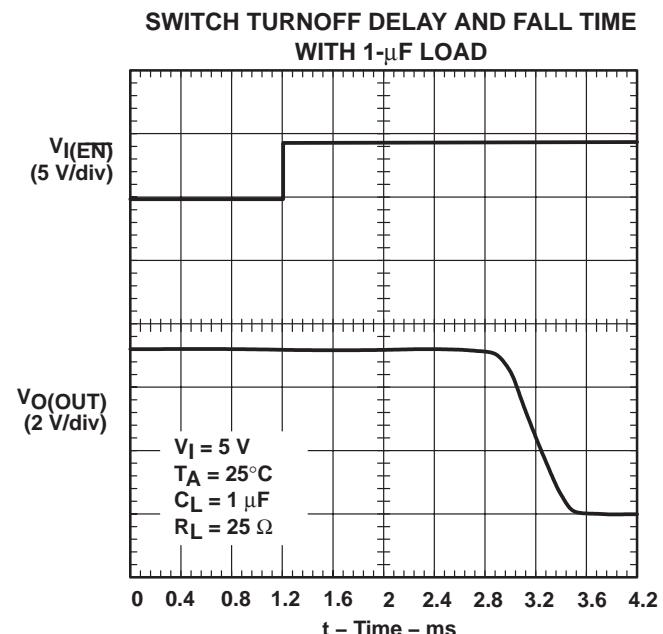

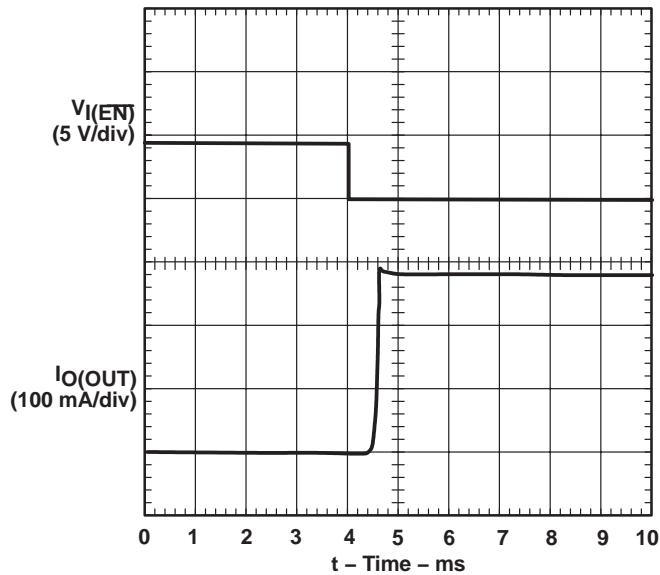

Figure 3

Figure 4

## TYPICAL CHARACTERISTICS

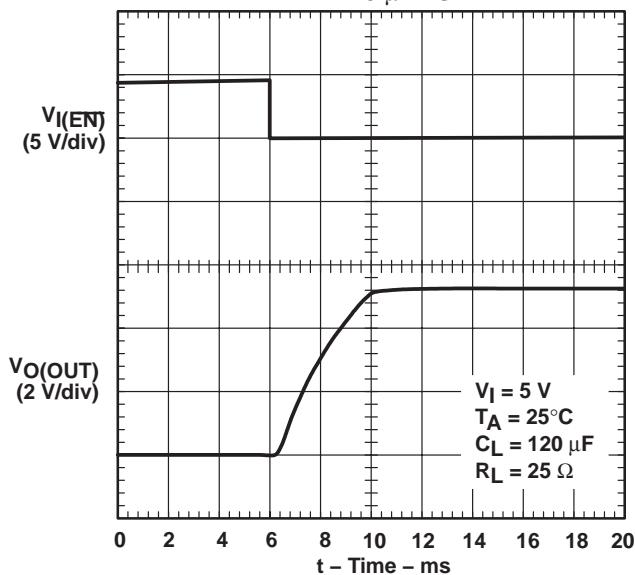

SWITCH TURNON DELAY AND RISE TIME

WITH 120- $\mu$ F LOAD

Figure 5

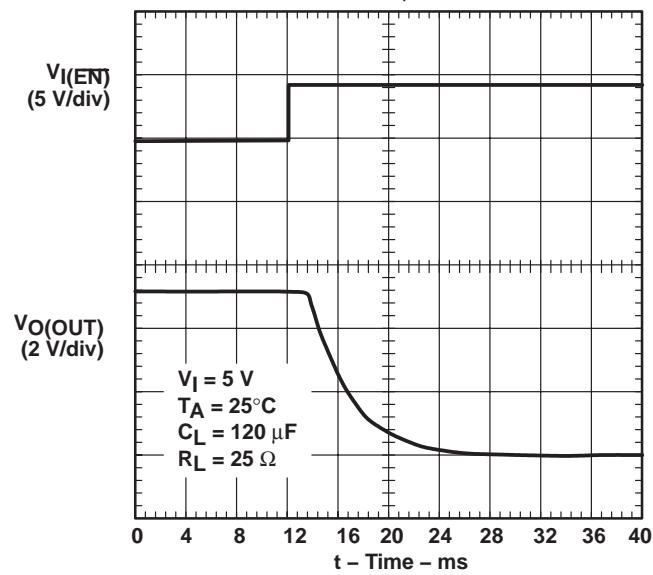

SWITCH TURNOFF DELAY AND FALL TIME

WITH 120- $\mu$ F LOAD

Figure 6

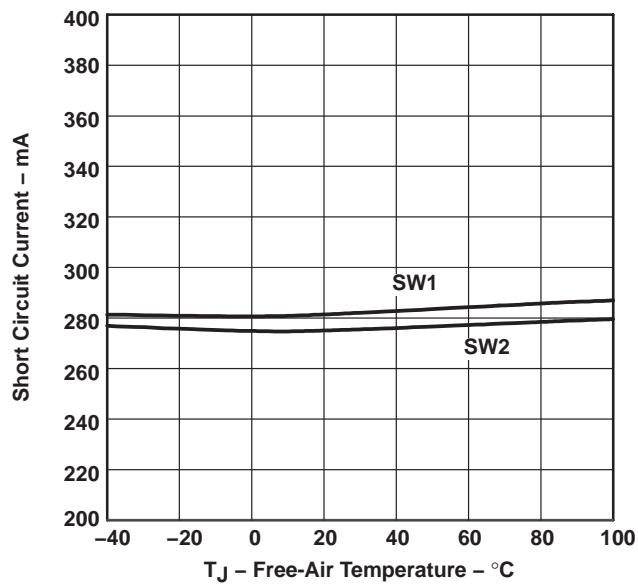

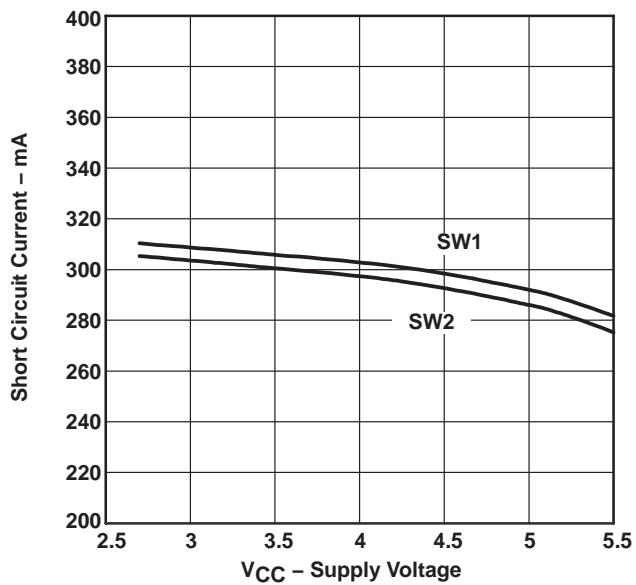

SHORT-CIRCUIT CURRENT, SWITCH

ENABLED INTO A SHORT

Figure 7

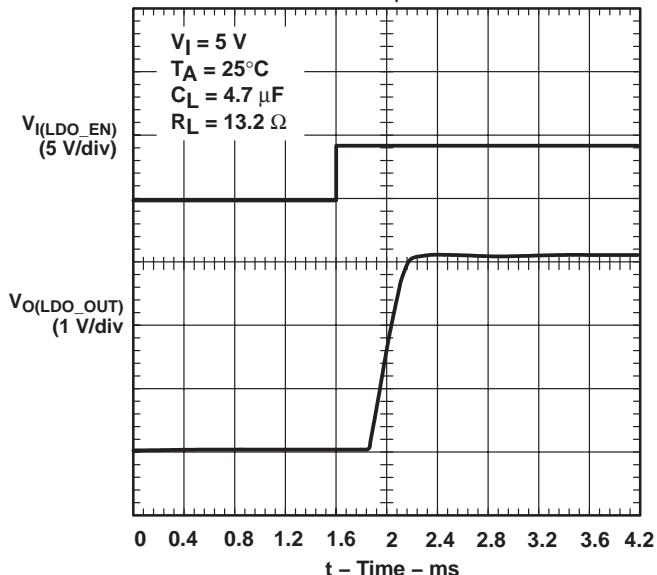

LDO TURNON DELAY AND RISE TIME

WITH 4.7- $\mu$ F LOAD

Figure 8

## TYPICAL CHARACTERISTICS

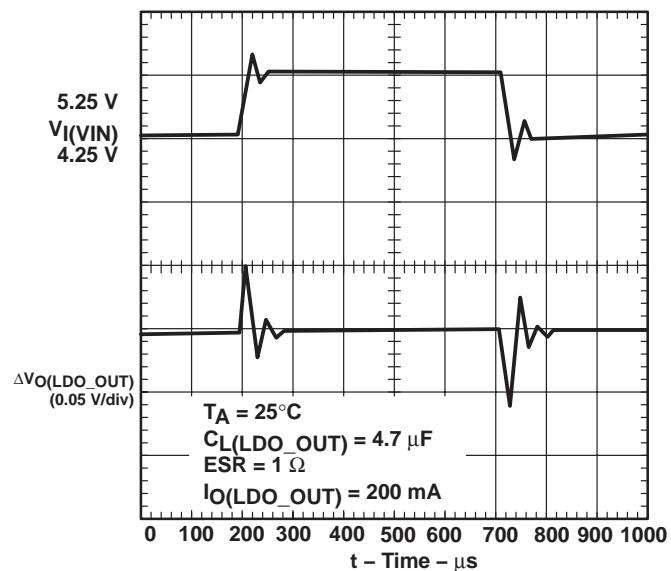

### LINE TRANSIENT RESPONSE

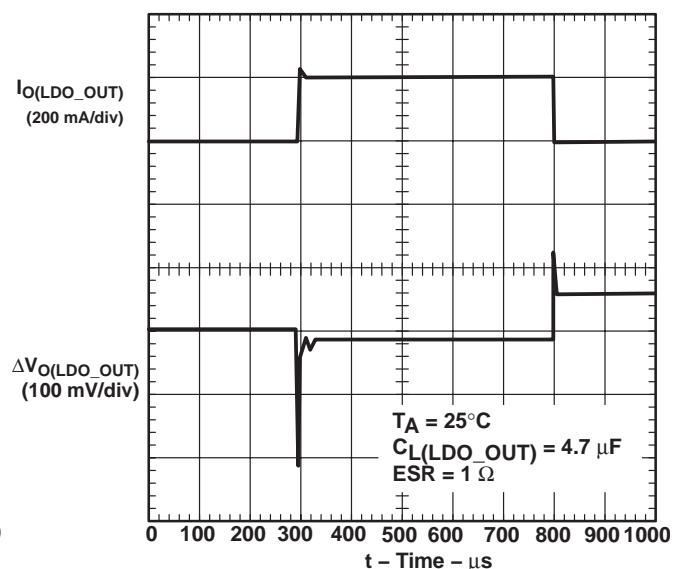

### LOAD TRANSIENT RESPONSE

Figure 9

Figure 10

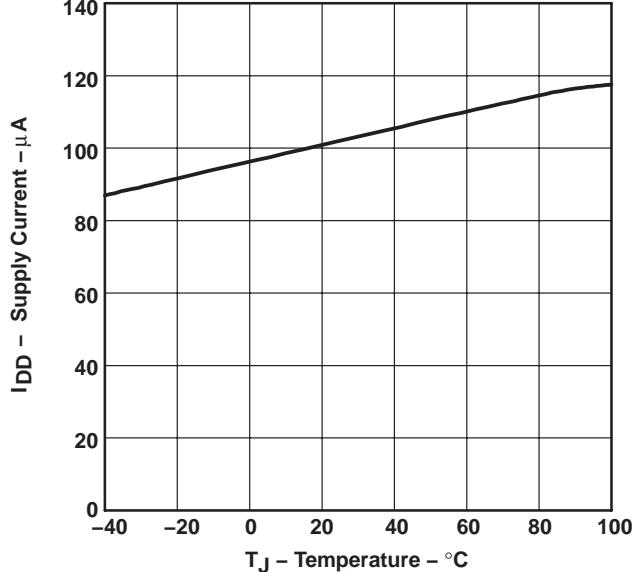

### SUPPLY CURRENT VS JUNCTION TEMPERATURE

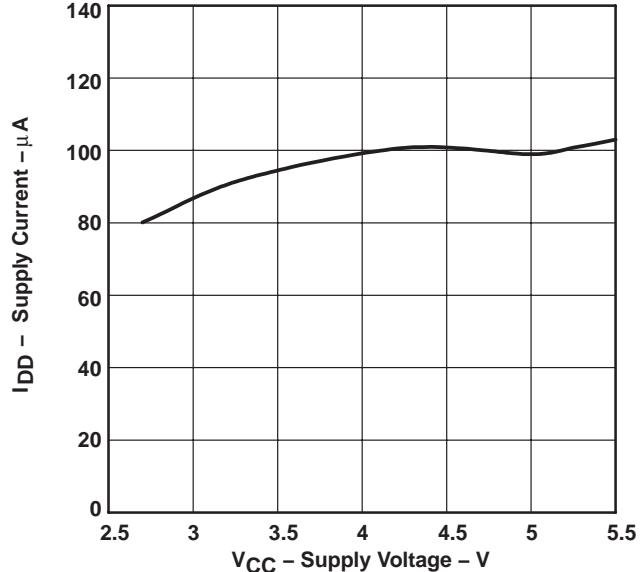

### SUPPLY CURRENT VS SUPPLY VOLTAGE

## TYPICAL CHARACTERISTICS

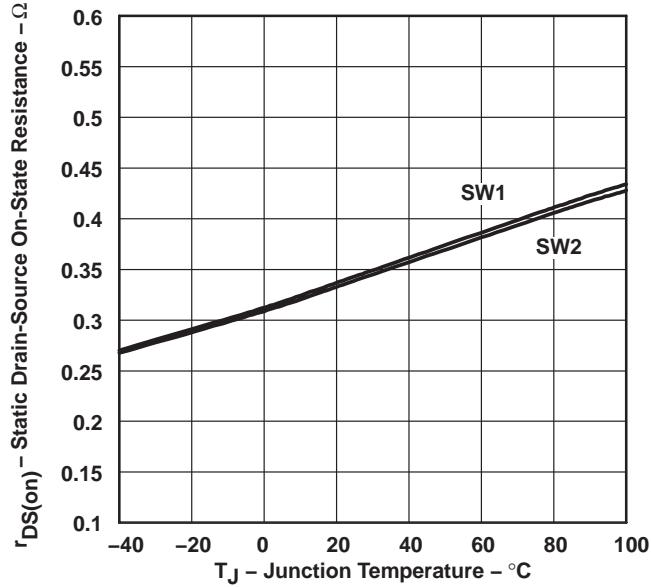

STATIC DRAIN-SOURCE ON-STATE RESISTANCE

vs

JUNCTION TEMPERATURE

Figure 13

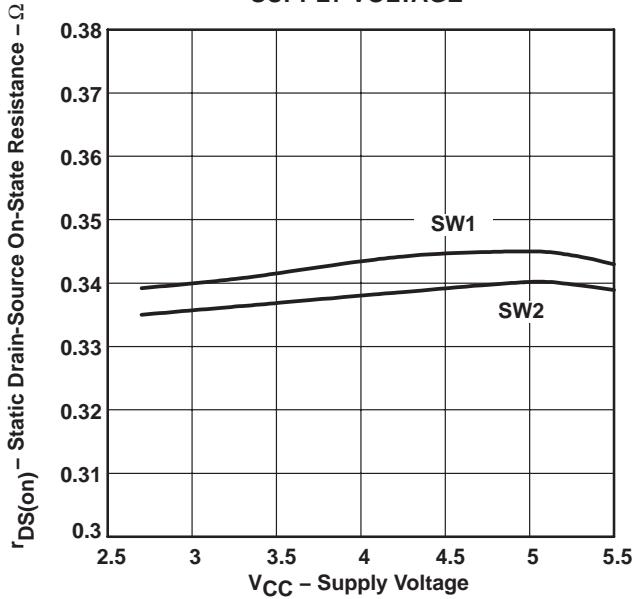

STATIC DRAIN-SOURCE ON-STATE RESISTANCE

vs

SUPPLY VOLTAGE

Figure 14

SHORT CIRCUIT CURRENT

vs

JUNCTION TEMPERATURE

Figure 15

SHORT CIRCUIT CURRENT

vs

SUPPLY VOLTAGE

Figure 16

---

TYPICAL CHARACTERISTICS

Figure 17

---

APPLICATION INFORMATION**external capacitor requirements on power lines**

Ceramic bypass capacitors (0.01- $\mu$  to 0.1- $\mu$ ) between VIN/SWIN1 and GND and SWIN2 and GND, close to the device, are recommended to improve load transient response and noise rejection.

Bulk capacitors (4.7- $\mu$ F) between VIN/SWIN1 and GND and between SWIN2 and GND are also recommended, especially if load transients in the hundreds of millamps with fast rise times are anticipated.

A 66- $\mu$ F bulk capacitor is recommended from OUTx to ground, especially when the output load is heavy. This precaution helps reduce transients seen on the power rails. Additionally, bypassing the outputs with a 0.1- $\mu$ F ceramic capacitor improves the immunity of the device to short-circuit transients.

**LDO output capacitor requirements**

Stabilizing the internal control loop requires an output capacitor connected between LDO\_OUT and GND. The minimum recommended capacitance is a 4.7  $\mu$ F with an ESR value between 200 m $\Omega$  and 10  $\Omega$ . Solid tantalum electrolytic, aluminum electrolytic and multilayer ceramic capacitors are all suitable, provided they meet the ESR requirements.

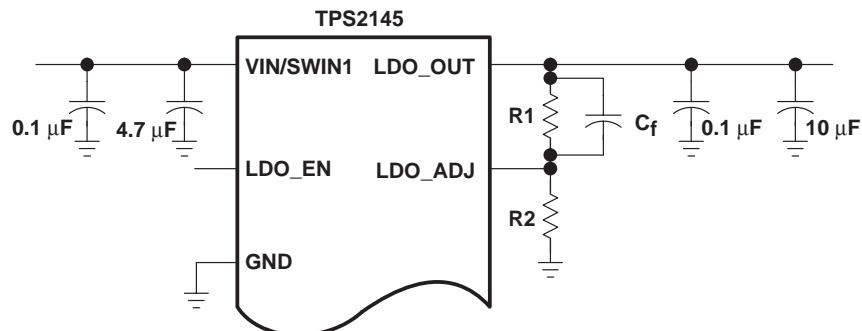

The adjustable LDO (for voltages lower than 3 V) requires a bypass capacitor across the feedback resistor as shown in Figure 18. The value of this capacitor is determined by using the following equation:

$$C_f = \frac{1}{(63.7e^3 \times 2 \times 3.14 \times R1)} - 4 \text{ pf} \quad (1)$$

where R1 is derived by programming the adjustable LDO (see programming the adjustable LDO regulator section shown below).

## APPLICATION INFORMATION

### programming the adjustable LDO regulator

The output voltage of the TPS2145 adjustable regulator is programmed using an external resistor divider as shown in Figure 18. The output voltage is calculated using:

$$\text{LDO\_OUT} = V_{\text{ref}} \left( 1 + \frac{R_1}{R_2} \right) \quad (2)$$

where  $V_{\text{ref}} = 0.8 \text{ V}$  typical (internal reference voltage).

Resistors R1 and R2 should be chosen for approximately  $4\text{-}\mu\text{A}$  (minimum) divider current. Lower value resistors can be used but offer no inherent advantage and waste more power. Higher values should be avoided as a minimum load is required to sink the LDO forward leakage and maintain regulation. The recommended design procedure is to choose  $R_2 = 200 \text{ k}\Omega$  to set the divider current at  $4\text{-}\mu\text{A}$  and then solve the LDO\_OUT equation for R1.

Figure 18. External Resistor Divider

#### OUTPUT VOLTAGE PROGRAMMING GUIDE

| OUTPUT VOLTAGE | R1     | R2     | C <sub>fb</sub> |

|----------------|--------|--------|-----------------|

| 3.3            | 625 kΩ | 200 kΩ | NR†             |

| 3.0            | 550 kΩ | 200 kΩ | NR†             |

| 2.5            | 425 kΩ | 200 kΩ | 2 pf            |

| 1.8            | 250 kΩ | 200 kΩ | 6 pf            |

| 1.5            | 175 kΩ | 200 kΩ | 10.3 pf         |

| 1.0            | 50 kΩ  | 200 kΩ | 46 pf           |

† NR – Not required

### overcurrent

A sense FET is used to measure current through the device. Unlike current-sense resistors, sense FETs do not increase the series resistance of the current path. When an overcurrent condition is detected, the device maintains a constant output current. Complete shutdown occurs only if the fault is present long enough to activate thermal limiting.

Three possible overload conditions can occur. In the first condition, the output is shorted before the device is enabled or before VIN has been applied. The TPS2145 and TPS2147 sense the short and immediately switch to a constant-current output.

In the second condition, the short occurs while the device is enabled. At the instant the short occurs, very high currents may flow for a very short time before the current-limit circuit can react. After the current-limit circuit has tripped (reached the overcurrent trip threshold), the device switches into constant-current mode.

---

## APPLICATION INFORMATION

### overcurrent (continued)

In the third condition, the load has been gradually increased beyond the recommended operating current. The current is permitted to rise until the current-limit threshold is reached or until the thermal limit of the device is exceeded. The TPS2145 and TPS2147 are capable of delivering current up to the current-limit threshold without damaging the device. Once the threshold has been reached, the device switches into its constant-current mode.

### OC response

The  $\overline{OCx}$  open-drain output is asserted (active low) when an overcurrent condition is encountered. The output will remain asserted until the overcurrent condition is removed. Connecting a heavy capacitive load to an enabled device can cause momentary false overcurrent reporting from the inrush current flowing through the device, charging the downstream capacitor. The TPS2145 and TPS2147 are designed to reduce false overcurrent reporting. An internal overcurrent transient filter eliminates the need for external components to remove unwanted pulses. Using low-ESR electrolytic capacitors on OUTx lowers the inrush current flow through the device during hot-plug events by providing a low-impedance energy source, also reducing erroneous overcurrent reporting.

### power dissipation and junction temperature

The major source of power dissipation for the TPS2145 and TPS2147 comes from the internal voltage regulator and the N-channel MOSFETs. Checking the power dissipation and junction temperature is always a good design practice and it starts with determining the  $r_{DS(on)}$  of the N-channel MOSFET according to the input voltage and operating temperature. As an initial estimate, use the highest operating ambient temperature of interest and read  $r_{DS(on)}$  from the graphs shown in the Typical Characteristics section of this data sheet. Using this value, the power dissipation per switch can be calculated using:

$$P_D = r_{DS(on)} \times I^2 \quad (3)$$

Multiply this number by two to get the total power dissipation coming from the N-channel MOSFETs.

The power dissipation for the internal voltage regulator is calculated using:

$$P_D = (V_I - V_{O(min)}) \times I_O \quad (4)$$

The total power dissipation for the device becomes:

$$P_{D(\text{total})} = P_D(\text{voltage regulator}) + (2 \times P_D(\text{switch})) \quad (5)$$

Finally, calculate the junction temperature:

$$T_J = P_D \times R_{\theta JA} + T_A \quad (6)$$

Where:

$T_A$  = Ambient Temperature  $^{\circ}\text{C}$

$R_{\theta JA}$  = Thermal resistance  $^{\circ}\text{C}/\text{W}$ , equal to inverting the derating factor found on the power dissipation table in this data sheet.

Compare the calculated junction temperature with the initial estimate. If they do not agree within a few degrees, repeat the calculation, using the calculated value as the new estimate. Two or three iterations are generally sufficient to get a reasonable answer.

---

## APPLICATION INFORMATION

### thermal protection

Thermal protection prevents damage to the IC when heavy-overload or short-circuit faults are present for extended periods of time. The faults force the TPS2145 and TPS2147 into constant-current mode at first, which causes the voltage across the high-side switch to increase; under short-circuit conditions, the voltage across the switch is equal to the input voltage. The increased dissipation causes the junction temperature to rise to high levels.

The protection circuit senses the junction temperature of the switch and shuts it off. Hysteresis is built into the thermal sense circuit, and after the device has cooled approximately 10 degrees, the switch turns back on. The switch continues to cycle in this manner until the load fault or input power is removed.

The TPS2145 and TPS2147 implement a dual thermal trip to allow fully independent operation of the power distribution switches. In an overcurrent or short-circuit condition, the junction temperature will rise. Once the die temperature rises to approximately 120°C, the internal thermal-sense circuitry checks to determine which power switch is in an overcurrent condition and turns that power switch off, thus isolating the fault without interrupting operation of the adjacent power switch. Should the die temperature exceed the first thermal trip point of 120°C and reach 155°C, the device will turn off.

### undervoltage lockout (UVLO)

An undervoltage lockout ensures that the device (LDO and switches) is in the off state at power up. The UVLO will also keep the device from being turned on until the power supply has reached the start threshold (see undervoltage lockout table), even if the switches are enabled. The UVLO will also be activated whenever the input voltage falls below the stop threshold as defined in the undervoltage lockout table. This function facilitates the design of hot-insertion systems where it is not possible to turn off the power switches before input power is removed. Upon reinsertion, the power switches will be turned on with a controlled rise time to reduce EMI and voltage overshoots.

### universal serial bus (USB) applications

The universal serial bus (USB) interface is a multiplexed serial bus operating at either 12-Mb/s, or 1.5-Mb/s for USB 1.1, or 480 Mb/s for USB 2.0. The USB interface is designed to accommodate the bandwidth required by PC peripherals such as keyboards, printers, scanners, and mice. The four-wire USB interface was conceived for dynamic attach-detach (hot plug-unplug) of peripherals. Two lines are provided for differential data, and two lines are provided for 5-V power distribution.

USB data is a 3.3-V level signal, but power is distributed at 5 V to allow for voltage drops in cases where power is distributed through more than one hub across long cables. Each function must provide its own regulated 3.3-V from the 5-V input or its own internal power supply.

The USB specification defines the following five classes of devices, each differentiated by power-consumption requirements:

- Hosts/self-powered hubs (SPH)

- Bus-powered hubs (BPH)

- Low-power, bus-powered functions

- High-power, bus-powered functions

- Self-powered functions

The TPS2145 and TPS2147 are well suited for USB hub and peripheral applications. The internal LDO can be used to provide the 3.3-V power needed by the controller while the dual switches distribute power to the downstream functions.

---

## APPLICATION INFORMATION

### USB power-distribution requirements

USB can be implemented in several ways, and, regardless of the type of USB device being developed, several power-distribution features must be implemented.

- Hosts/self-powered hubs must:

- Current-limit downstream ports

- Report overcurrent conditions on USB  $V_{BUS}$

- Bus-powered hubs must:

- Enable/disable power to downstream ports

- Power up at  $<100$  mA

- Limit inrush current ( $<44$   $\Omega$  and  $10$   $\mu F$ )

- Functions must:

- Limit inrush currents

- Power up at  $<100$  mA

The feature set of the TPS2145 and TPS2147 allows them to meet each of these requirements. The integrated current-limiting and overcurrent reporting is required by hosts and self-powered hubs. The logic-level enable and controlled rise times meet the need of both input and output ports on bus-powered hubs, as well as the input ports for bus-powered functions.

### USB applications

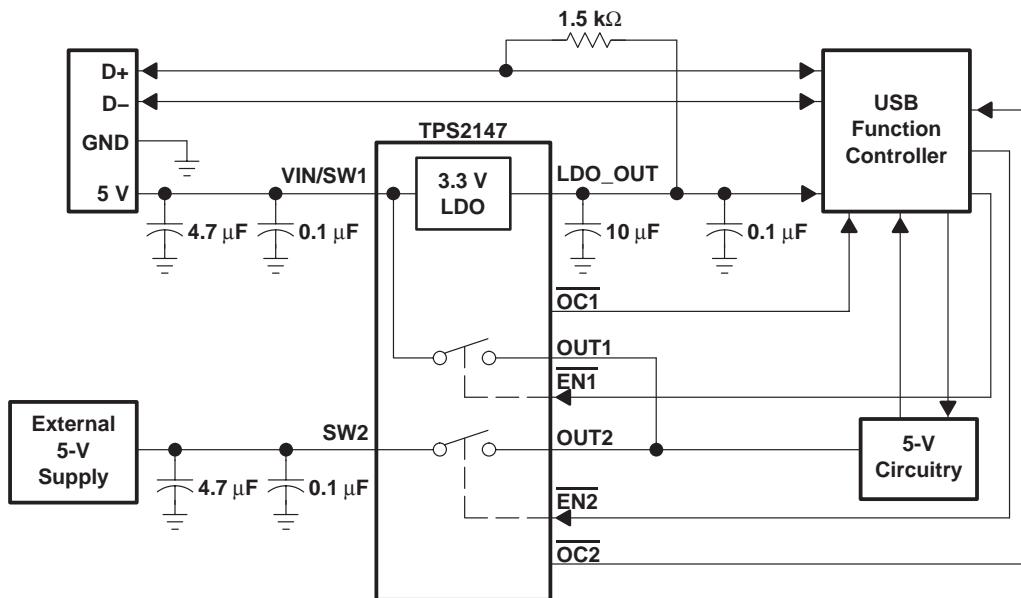

Figure 19 shows the TPS2147 being used in a USB bus-powered/self-powered peripheral design. The internal 3.3-V LDO is used to provide power for the USB function controller as well as to the 1.5-k $\Omega$  pullup resistor.

In bus-powered mode, switch 1 provides power to the 5-V circuitry. In self-powered mode, switch 2 provides power to the 5-V circuitry while the USB 5-V still provides power to the 3.3-V LDO (USB allows self-powered devices to draw up to 100 mA from  $V_{BUS}$ ).

## APPLICATION INFORMATION

Figure 19. TPS2147 USB Bus-Powered/Self-Powered Peripheral Application

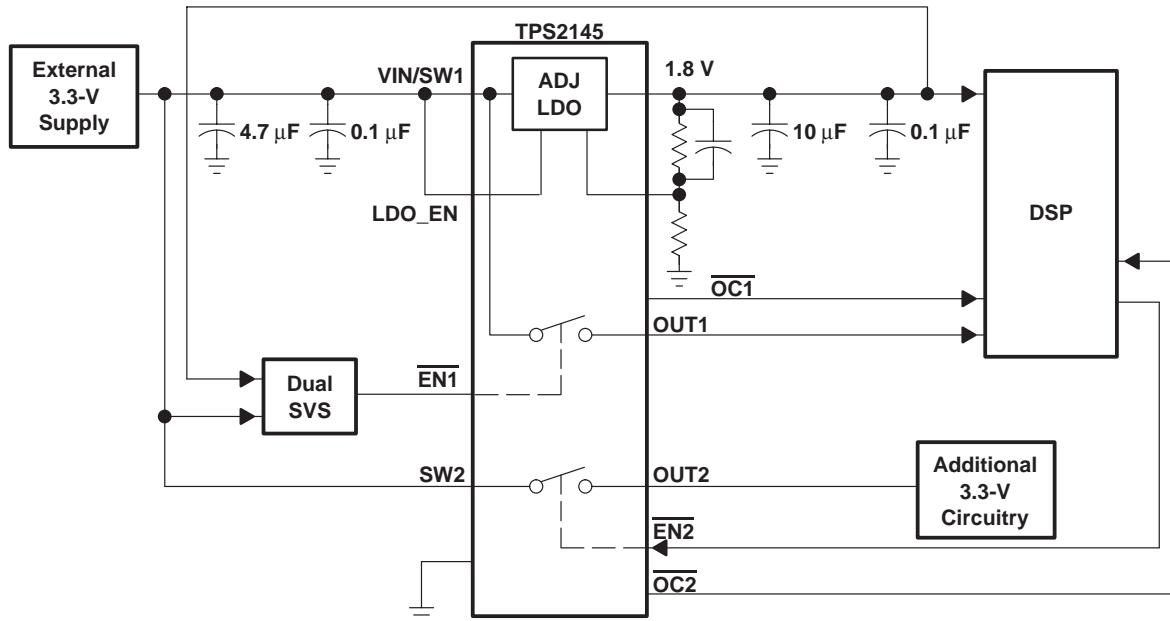

### DSP applications

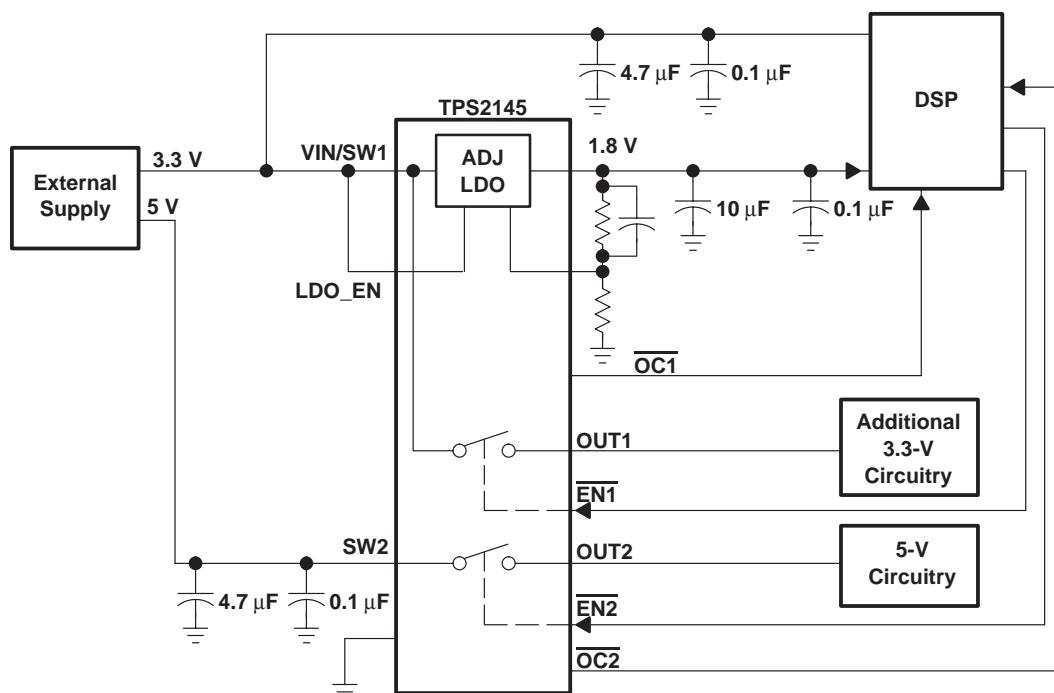

Figure 20 shows the TPS2145 in a DSP application. DSPs use a 1.8-V core voltage and a 3.3-V I/O voltage. In this type of application, the TPS2145 adjustable LDO is configured for a 1.8-V output specifically for the DSP core voltage.

The additional 3.3-V circuitry is powered through switch 1 of the TPS2145 only after the DSP is up and running. Switch 2 is used to provide power to additional circuitry operating from a different voltage source. This switch is also controlled by the DSP.

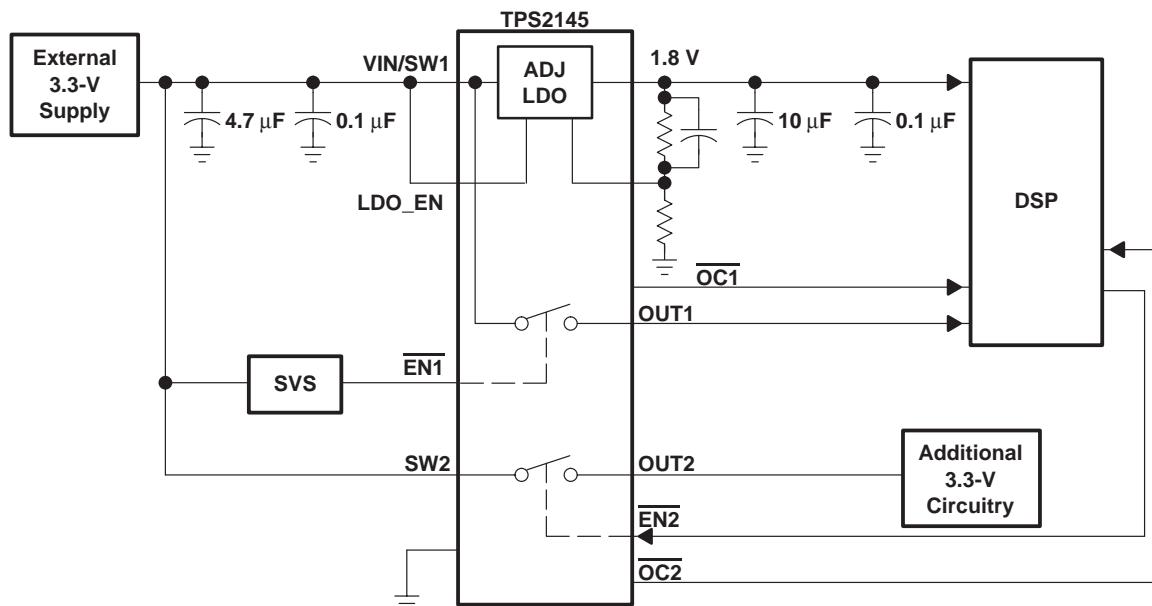

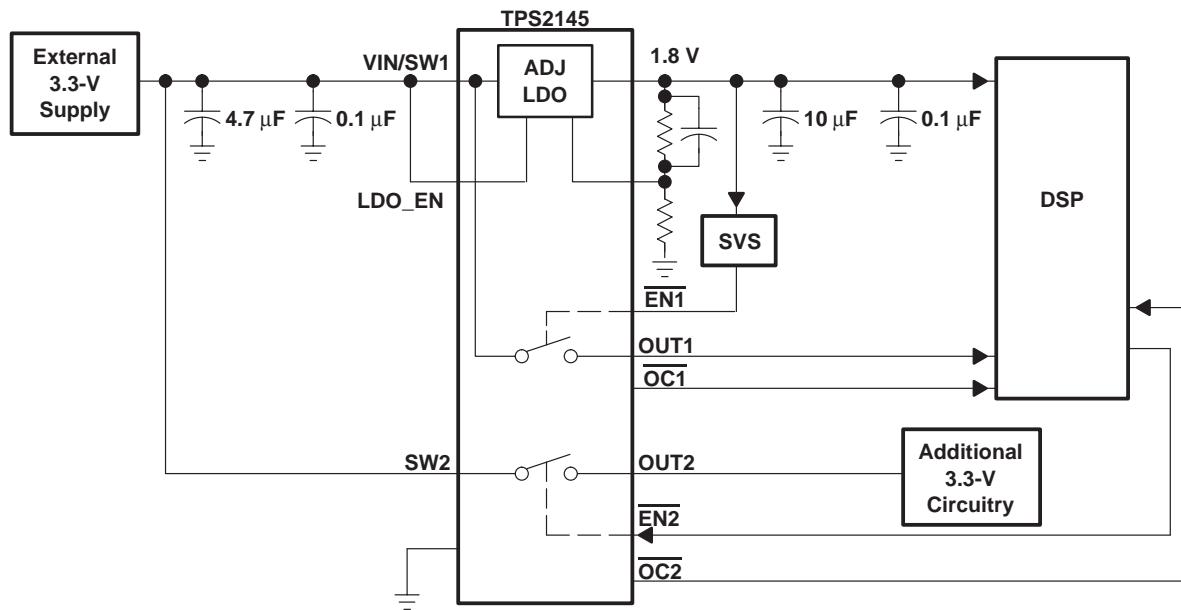

Figures 21 thru 23 show the TPS2145 in various DSP applications using a supply voltage supervisor (SVS) chip to control the enable for the 3.3 V powering up the DSP I/O circuitry.

## APPLICATION INFORMATION

Figure 20. TPS2145 DSP Application

Figure 21. TPS2145 DSP With SVS Application

## APPLICATION INFORMATION

Figure 22. TPS2145 DSP With SVS Application

Figure 23. TPS2145 DSP With Dual SVS Application

---

## APPLICATION INFORMATION

### power supply sequencing

DSPs typically do not require specific power sequencing between the core supply and the I/O supply. However, systems should be designed to ensure that neither supply is powered up for extended periods of time if the other supply is below the proper operating voltage.

### system level design consideration

System level design considerations, such as bus contention, may require supply sequencing to be implemented. In this case, the core supply should be powered up at the same time as, or prior to (and powered down after), the I/O buffers. This is to ensure that the I/O buffers receive valid inputs from the core before the output buffers are powered up, thus, preventing bus contention with other chips on the board.

### power supply design consideration

For some DSP systems, the core supply may be required to provide a considerable amount of current until the I/O supply is powered up. This extra current condition is a result of uninitialized logic within the DSP(s). Decreasing the amount of time between the core supply power up and the I/O supply power up can minimize the effects of this current draw.

**PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package Drawing | Pins | Package Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples                                                                         |

|------------------|---------------|--------------|-----------------|------|-------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------------------------------------------------------------------------------|

| TPS2147IDGQ      | ACTIVE        | HVSSOP       | DGQ             | 10   | 80          | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 85    | AWL                     | <span style="background-color: red; color: white; padding: 2px;">Samples</span> |

| TPS2147IDGQG4    | ACTIVE        | HVSSOP       | DGQ             | 10   | 80          | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 85    | AWL                     | <span style="background-color: red; color: white; padding: 2px;">Samples</span> |

| TPS2147IDGQR     | ACTIVE        | HVSSOP       | DGQ             | 10   | 2500        | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 85    | AWL                     | <span style="background-color: red; color: white; padding: 2px;">Samples</span> |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) **RoHS:** TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

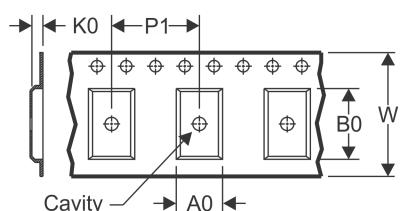

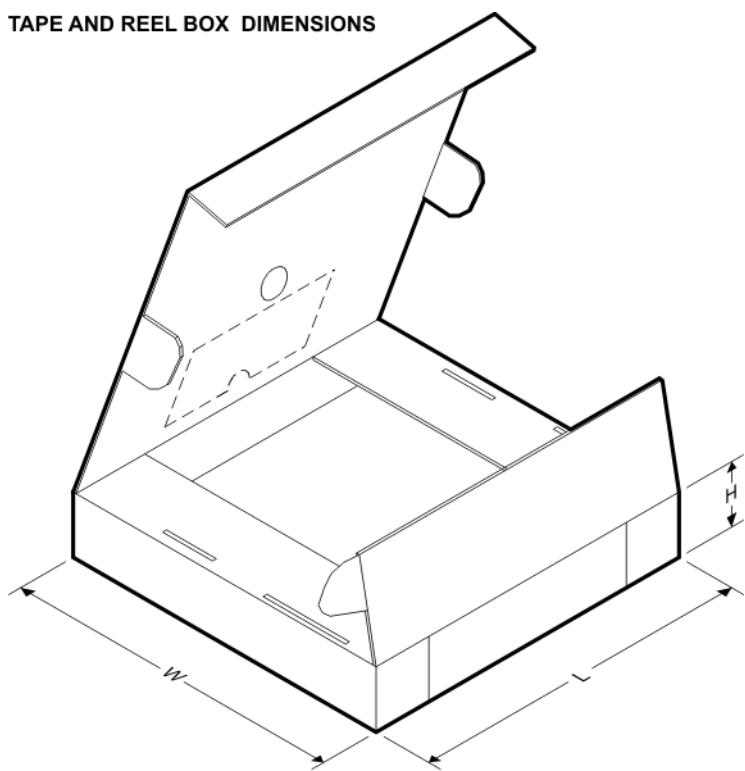

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| TPS2147IDGQR | HVSSOP       | DGQ             | 10   | 2500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS2147IDGQR | HVSSOP       | DGQ             | 10   | 2500 | 358.0       | 335.0      | 35.0        |

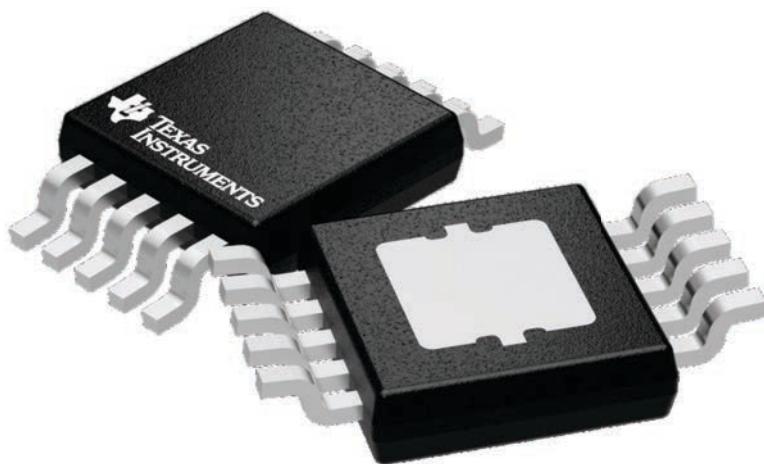

## GENERIC PACKAGE VIEW

**DGQ 10**

**PowerPAD™ HVSSOP - 1.1 mm max height**

3 x 3, 0.5 mm pitch

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4224775/A

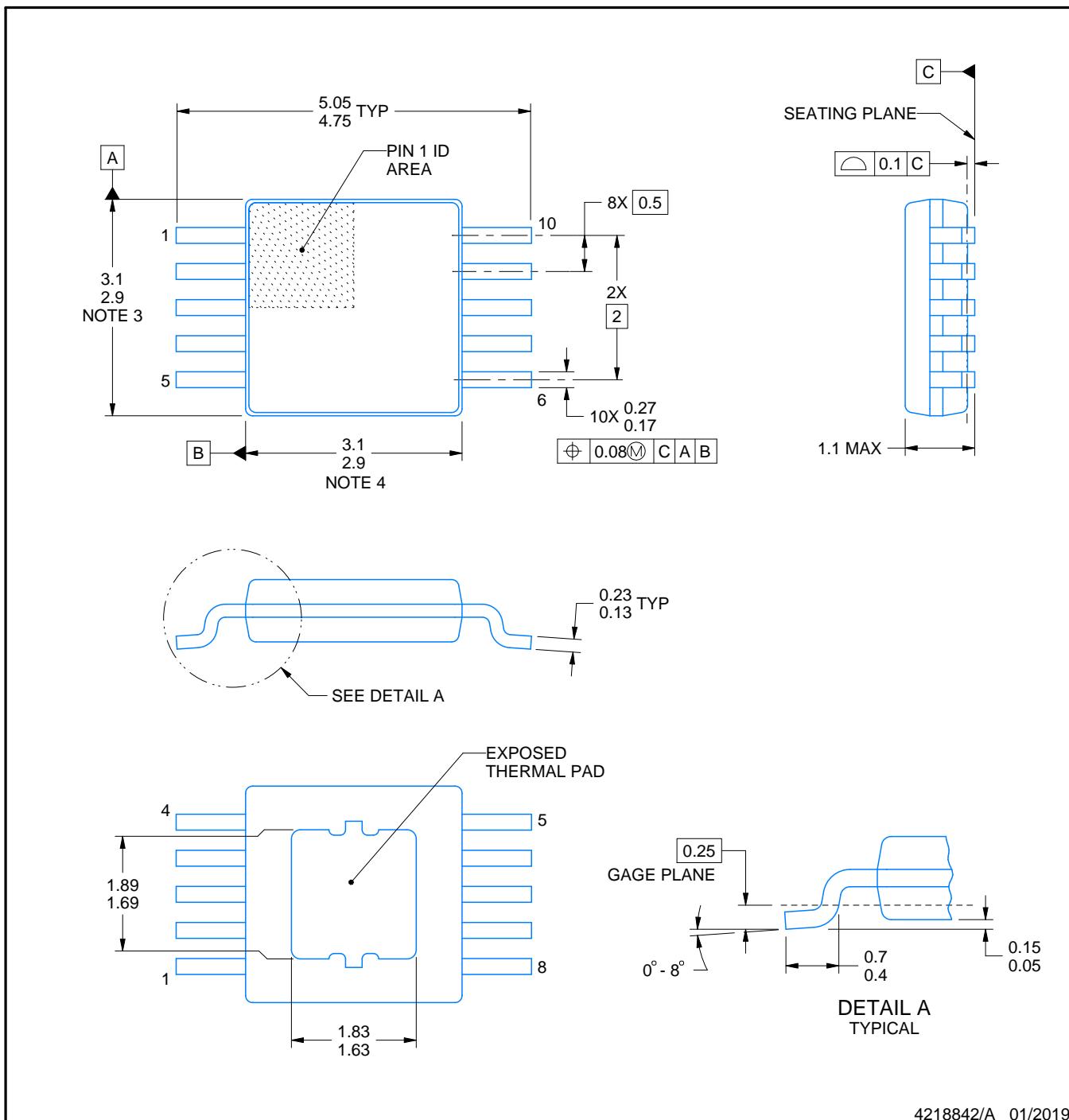

# PACKAGE OUTLINE

DGQ0010D

PowerPAD™ - 1.1 mm max height

PLASTIC SMALL OUTLINE

4218842/A 01/2019

PowerPAD is a trademark of Texas Instruments.

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MO-187, variation BA-T.

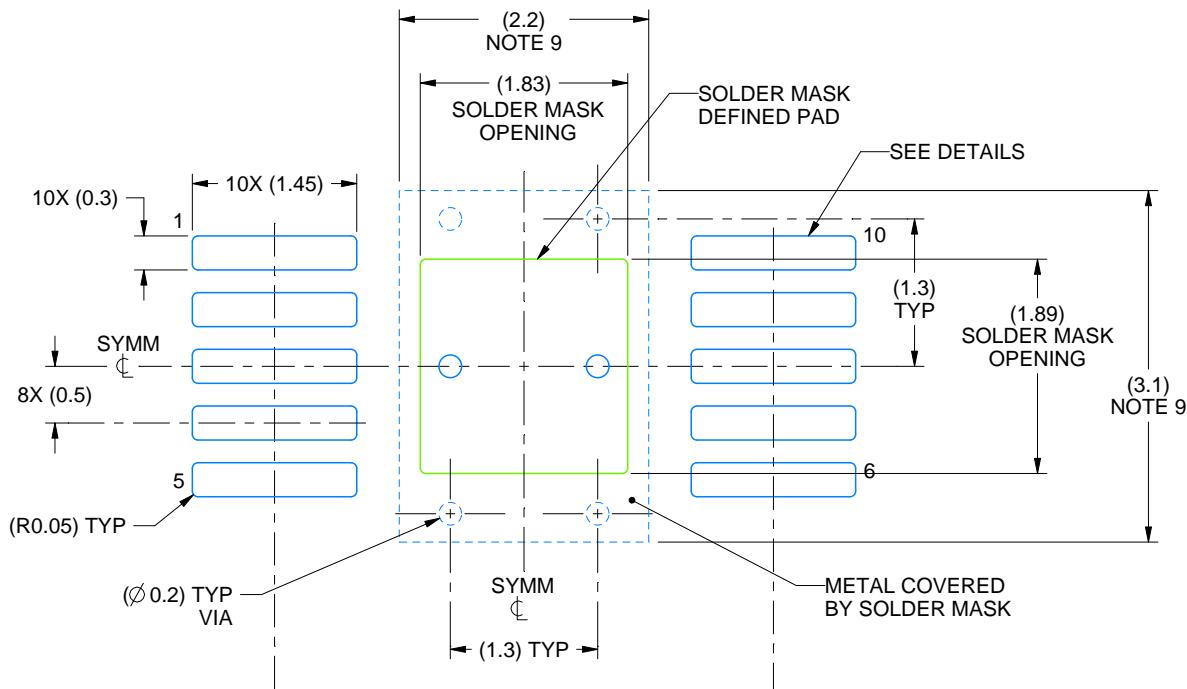

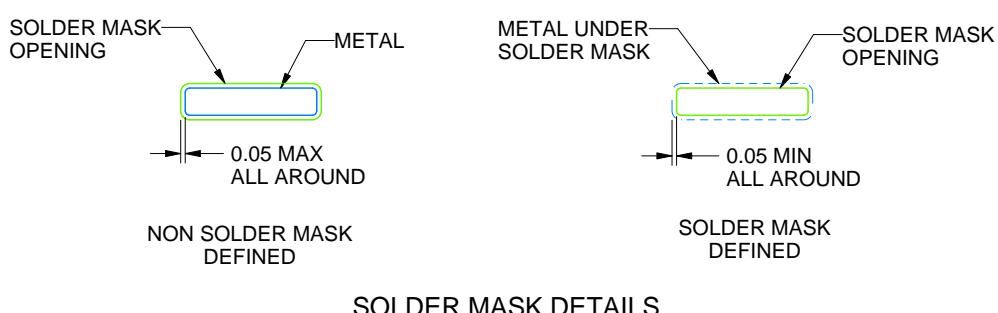

# EXAMPLE BOARD LAYOUT

DGQ0010D

PowerPAD™ - 1.1 mm max height

PLASTIC SMALL OUTLINE

LAND PATTERN EXAMPLE

SCALE:15X

SOLDER MASK DETAILS

4218842/A 01/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

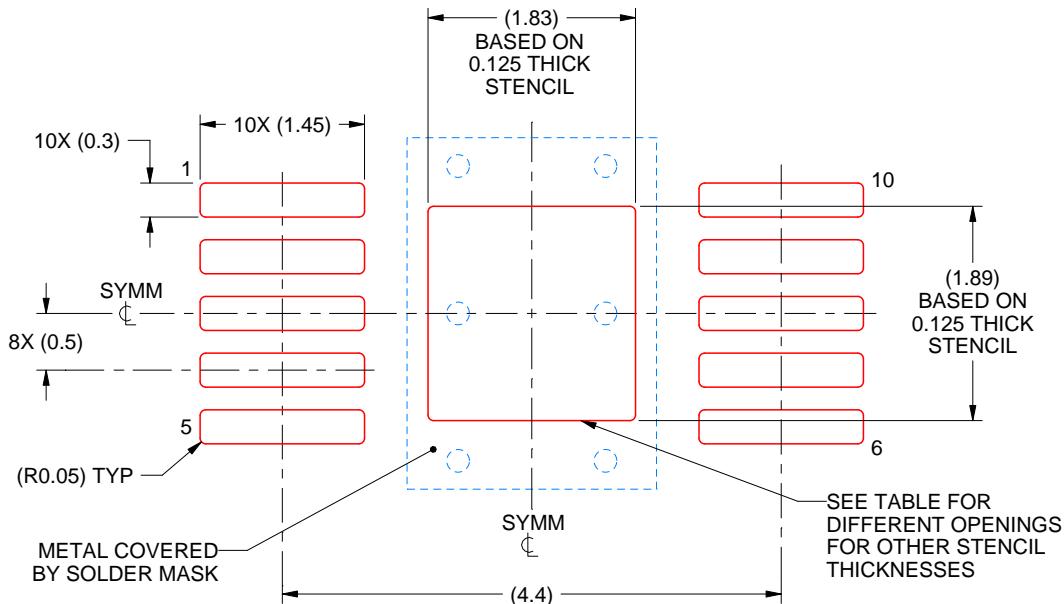

# EXAMPLE STENCIL DESIGN

DGQ0010D

PowerPAD™ - 1.1 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:15X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 2.05 X 2.11            |

| 0.125             | 1.83 X 1.89 (SHOWN)    |

| 0.150             | 1.67 X 1.73            |

| 0.175             | 1.55 X 1.60            |

4218842/A 01/2019

NOTES: (continued)

10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

11. Board assembly site may have different recommendations for stencil design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<https://www.ti.com/legal/termsofsale.html>) or other applicable terms available either on [ti.com](https://ti.com) or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2021, Texas Instruments Incorporated